ATF1504芯片的接口和功能研究(通信论文)

ATF1504芯片的接口和功能研究

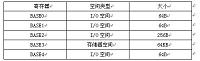

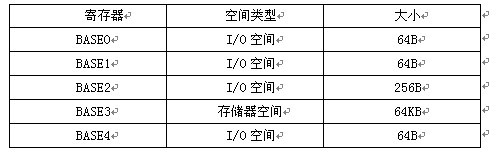

4.1.1 ATF1504芯片[6]概述

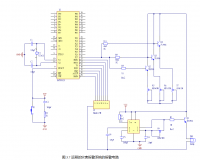

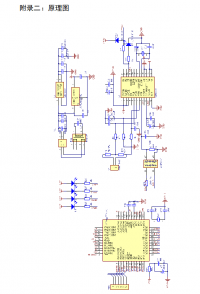

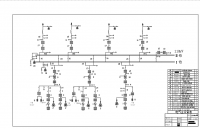

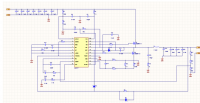

ATF1504(见附录2)是一个告诉的,高密度的,复杂的可编程逻辑设备(CPLD),它使用了ATMEL公司成熟的电可擦除存储器技术.它有64个逻辑宏单元并有36个I/O引脚.它可以很容易的将多个TTL,SSI,MSI,LSI和Classic PLDS集成为具有一定功能的逻辑. ATF1504的强大的循序开关矩阵交换电路增加了可使用的门数,同时也增加了成功进行引脚锁定的设计更正的可能性. ATF1504有36个双向的I/O引脚和4个专门的输入引脚,这个引脚取决于设备选择包的类型.每一个专门的引脚可同时作为一个全局控制信号,寄存器时钟,寄存器重置或输出使能.这些控制信号中的没一个都可以选取单独用于每一个宏单元.

64个宏单元中的任一个都能产生一个隐藏的反馈至全局总线.每个输入和I/O引脚同样要进入全局总线.在每个逻辑块中的开关矩阵交换电路选取来自全局总线的40个单个信号.每个宏单元同时产生一个反馈逻辑进入一个区域总线周期.在ATF1504的宏单元间的CASCADE逻辑可以快速,高效的生成复杂的逻辑功能. ATF1504拥有4个这样的逻辑链,每个逻辑链都能用40个Product Terms中的一个扇入来生成Sum Term逻辑.

ATF1504的宏单元有足够的弹性来支持一个高复杂性,高速运行的逻辑功能.每个宏单元包括5个部分:Product Terms和Product Term多路选择器,OR/XOR/CASCADE逻辑,一个flip-flop,数促选择和使能,以及逻辑阵列输入.未使用的Product Terms由编译器自动使之无效,以减少功耗,一个安全熔丝,在编程是会保护ATF1504中的内容.两个字节(16位)的用户签名为用户可访问的,它的作用是用来存储工程名,部分号,修正或日期记录.用户签名的访问与安全熔丝的状态无关.ATF1504设备是一个在系统可编程的(ISP)设备.它使用工业标准4引脚的JTAG接口(IEEE std.1149.1),并且与JTAG的边界扫描描述语言(BSDL)是全兼容的.ISP允许设备在设备没有从印制电路板上移除的状态下进行编程.因此,简化了生产流程,ISP同时也允许使用软件来制作和设计.

4.1.2 ATF1504各功能模块的描述

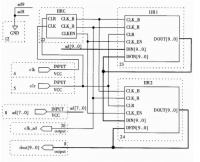

1. Product Terms多路选择器

每个ATF1504单元都有5个Product Terms.每两个Product Term作为可能的输入来接收同时来自全局总线和区域总线的所有信号.Product Term多路选择器(PTMUX)为宏单元的逻辑门和控制信号分配了5个必须的Product Term.PTMUX的编程取决于设计编译器.它会自动选择最佳的宏单元配置.

2. OR/XOR/CASCADE逻辑

ATF1504逻辑结构的设计可以高效的支持所有的逻辑类型.在单个宏单元中,所有的Product Terms能被部成OR门,生成一个5-input的AND/OR Sum Term.

借助于来自相邻宏单元的CASIN,这些逻辑门可扩展成40个只带有一点额外的延迟Product Terms.宏单元的XOR门可以进行高效的比较和算术功能.XOR的一个input来自OR Sum Term.另一个XOR input可作为一个Product Term或者是接高/低电平.对于组合outputs,固定电平input允许极性选择.对于寄存器功能,固定电平允许进行Product Terms的德摩根最小化.XOR门能与T型和JK型flip-flops.

3. Flip-flop

ATF1504的flip-flop具有非常弹性的数据和控制功能.数据输入可以来自独立的Product Term中的XOR门,也可以直接来自I/O引脚.选择独立的Product Term允许在组合的输出宏单元中生成一个寄存器的反馈.(这个特性由优化软件自动执行).此外,和D,T,JK和SR操作一样,flip-flop同样能为数据锁存之用.在这种模式下,数据在时钟为高电平是通过,在时钟低电平时锁存.时钟本身既可以作为全局时钟信号(GCK[0:2])之一,也可以作为一个独立的Product Term. flip-flop在时钟的上升沿改变状态.当GCK信号作为时钟信号时,宏单元的Product Term其中之一可以被用来作为时钟使能.当时钟使能功能有效,此时使能信号为低电平,所有的时钟边沿被忽略掉. flip-flop的异步重置(AR)信号既可以是一个Product Term的GCLEAR,也可以是总是关闭.AR可同时是Product Term的GCLEAR的一个逻辑OR.异步预重置(AP)可以是一个Product Term或者总是关闭.

4. Output 选择与使能

ATF1504的宏单元的输出可以作为寄存器输出或者组合输出.隐藏的反馈信号既可作为组合信号,也可作为寄存器信号,而不论输出是组合的还是寄存器的.多路输出使能器(MOE).控制输出使能信号.任何缓冲器可以永久的有效用于简单的输出操作.缓冲器同样也可以永久的无效从而允许将引脚用作输入.在这样的配置下,所有的宏单元资源依然是有效的,包括隐藏的反馈信号,扩展器和CASCADE逻辑.每个宏单元的输出使能既可被用做两个专用的OE输入引脚也可用做一个I/O输入引脚,或者作为一个独立的Product Term.

5. Global Bus/Switch Matrix

全局总线包括所有的inpu和I/O引脚信号,以及来自64个宏单元的隐藏反馈信号.在每个逻辑块中的开关矩阵交换电路尽可能的接收来自全局总线的所有信号.在软件控制下,40多个这种信号可以作为逻辑块得输入.

6. Foldback Bus

每个宏单元同样生成一个Foldback Product Term.这个信号进入区域总线,并且对于4个宏单元都有效. Foldback是宏单元的Product Term中的一个相反的极性.在每个区域中的16个Foldback Term允许生成高Fan-in sum terms并带有一般的附加延时.

7. Programmable Pin-Keeper Option for Inputs and I/Os

ATF1504提供对所有input和I/O引脚的编程属性从而可以利用Pin-Keeper电路。当任一引脚以高/低电平驱动,并随后左悬浮,它仍然会保持之前的高会低电平。这个电路可以阻止未被使用的input和I/O线由于悬空而影响电压,并由此而引起的不必要的功耗和系统噪声。Keeper电路的存在可以取消外部的上拉电阻和它们的DC功耗。

8. Speed/Power Management

ATF1504有多个内建的速度和电源管理特性。ATF1504设有一个电路。它可以在电路没有逻辑相互发生时自动将设备至于低源的可靠的模式。这样不仅减少了电路在空闲期的功耗而且能够工作在5MHz以下的尽可能多的应用提供适当的能量节约。这个特性可以作为一台设备的速度属性。

9. I/O Diagram

为了进一步减少功耗,每个ATF1504宏单元设置了一个Reduced Power比特位特性。这个特性允许独立的宏单元配置成最大能量节约。这也可以最为一台设备的选择选择。ATF1504同样有一个可选的Power-Down模式。在这个模式下,电流会降到10mA以下。当Power-Down属性选取后,不论PD1或者PD2引脚都可用作Power-Down的一部分。在设计资源文件里,Power-Down属性会被选取。当这属性有效时,不论PD1,PD2那个是高,设备都会进入Power-Down状态。在Power-Down模式下,所有的内部逻辑信号都被锁存和保持,作为任意的可输出引脚。一直到PD为Low,所有的引脚交互才生效,当Power-Down特性有效时,PD1或PD2引脚不能用作一个逻辑输入或输出。但是,引脚的宏单元仍然可用于生成隐藏的反馈和CASCADE逻辑信号。所有的Power-Down AC特性参数被来自外部的input或I/O引脚计算,此时Reduced Power位时开启的。对于在Reduced Power模式下的宏单元,Reduced Power adder tRPT,必需要被加到AC参数中,它包括数据路径,tLAD,tLAC,tIC,tACL,tACH和tSEXP.ATF1504宏单元同样有这个属性,由此能耗可以在每个宏单元的基础上减少。通过使Power-Down属性有效,那些没被使用的宏单元就可被关闭,从而就能减少整个设备的功耗。

微信

QQ1:3097331788 QQ2:2601997959 QQ3:2993773635