多速率滤波器的VHDL设计与实现

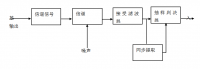

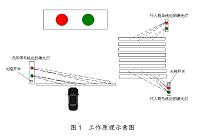

摘 要:数字滤波器是由数字乘法器、加法器和延时单元组成的一种装置。其功能是对输入离散信号的数字代码进行运算处理,以达到改变信号频谱的目的。由于电子计算机技术和大规模集成电路的发展,数字滤波器已可用计算机软件实现,也可用大规模集成数字硬件实时实现。数字信号处理在科学和工程技术许多领域中得到广泛的应用,与多速率滤波器相比,多速率滤波器可以用较低的阶数获得较高的选择性,故本课题采用一种基于FPGA的多速率滤波器的设计方案,首先分析了多速率滤波器的原理及设计方法,然后通过MAX+PLUSⅡ的设计平台,采用自顶向下的模块化设计思想将整个多速率滤波器分为:时序控制、延时、补码乘加和累加四个功能模块。分别对各模块采用VHDL进行描述后,进行了仿真和综合。仿真结果表明,本课题所设计的多速率滤波器运算速度较快,系数改变灵活,有较好的参考价值。

关键词:电子设计自动化,多速率滤波器,现场可编程门阵列,硬件描述语言

Absrtact: Digital filter is a device composed of digital multiplier, adder and delay unit. Its function is to calculate and process the digital code of the input discrete signal in order to change the signal spectrum. With the development of computer technology and large scale integrated circuits, digital filters can be realized by computer software or by large scale integrated digital hardware in real time. Digital signal processing has been widely used in many fields of science and engineering technology. Compared with multi-rate filter, multi-rate filter can obtain higher selectivity with lower order. Therefore, a design scheme of multi-rate filter based on FPGA is adopted in this paper. Firstly, the principle and design method of multi-rate filter are analyzed, and then the design platform of MAX+PLUS II is adopted. The whole multi-rate filter is divided into four functional modules: timing control, delay, complement multiplication and accumulation by using the top-down modular design idea. After describing each module with VHDL, simulation and synthesis are carried out. The simulation results show that the multi-rate filter designed in this paper has fast operation speed, flexible coefficient change and good reference value.

Key words: Electronic Design Automation, Multirate Filter, Field Programmable Gate Array, Hardware Description Language

目录

序 言 5

第一章 数字滤波器设计原理说明 6

1.1滤波器简介 6

1.2数字滤波器的分类 7

1.3数字滤波器的技术要求 8

1.4多速率滤波器设计 10

1.5 多速率滤波器的线性相位特性 10

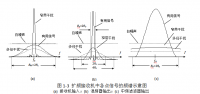

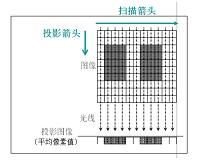

多速率滤波器的幅频特性 12

1.7基于窗函数的多速率滤波器设计 18

第2章 EDA技术和可编程逻辑器件 33

2. 1 电子设计自动化EDA技术 33

2. 2可编程逻辑器件 33

2.2.1可编程逻辑器件简介 33

2.2.2使用FPGA器件进行开发的优点 34

2.2.3 FPGA设计的开发流程 34

2.3 硬件描述语言VHDL及数字系统设计方法 35

2.3.1 硬件描述语言VHDL简介 35

2.3.2利用VHDL设计数字系统 35

第3章多速率滤波器的设计与仿真结果分析 37

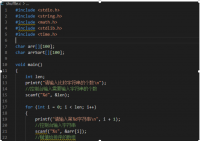

3.1 各模块的设计与仿真结果分析 37

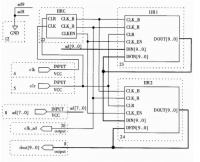

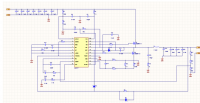

3.1.1 时序控制模块的设计与仿真结果分析 37

3.1.2 延时模块的设计与仿真结果分析 38

3.1.3 补码乘加模块的设计与仿真结果分析 38

3.1.4 累加模块的设计与仿真结果分析 40

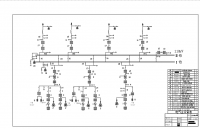

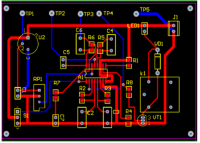

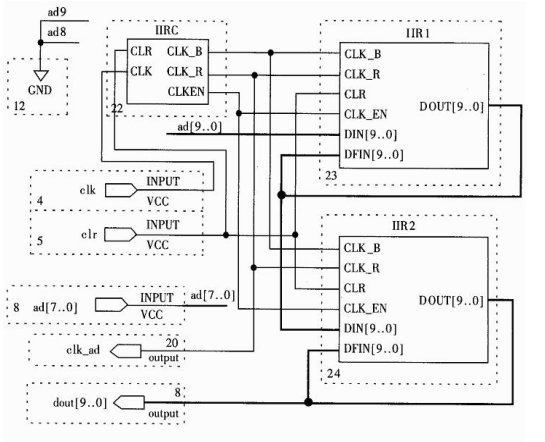

3.1.5 顶层模块设计 40

3.2 多速率滤波器的仿真与结果分析 41

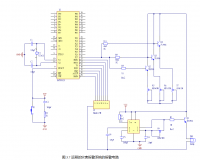

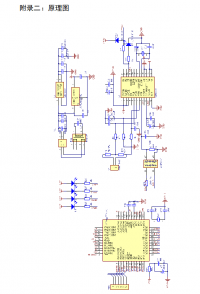

3.2.1 多速率滤波器的系统设计 41

3.2.2 多速率滤波器的系统仿真与结果分析 42

3.2.3 高阶多速率滤波器的实现 43

结 束 语 46

参考文献 47

参考文献

[1] 刘凌,胡永生译.数字信号处理的FPGA实现[M].北京:清华大学出版社.2003.

[2] 丁玉美,高西全.数字信号处理[M].西安:西安电子科技大学出版社.2004.

[3] 潘松,黄继业.EDA技术实用教程[M].北京:科学出版社.2000.

[4] 潘松,王国栋.VHDL实用教程[M].成都:电子科技大学出版社.2001.

[5] 倪向东.基于FPGA的四阶多速率滤波器[J].电子技术应用,2003.

[6] 王卫兵.高阶多速率滤波器的FPGA描述[J].电子元器件,2005,16期:pp3-4.

[7] 黄任.VHDL入门·解惑·经典实例·经验总结[M].北京:北京航空航天出版社.2005.

[8] 北京理工大学ASIC研究所.VHDL语言100例详解[M].北京:清华大学出版社.1999.

[9] Joseph B. Evans, "Efficient F1R Filter Architectures Suitable for FPGA Implementation"[M]. IEEE Trans, Circuits and System,July 1994.

[10]Javier Valls, Marcos M. Peiro, Trini Sansaloni, Eduardo Boemo, "A Study About FPGA-BasedDigital Filters"[J], IEEE SIPS, pp191-201,October 1998.