基于EDA的序列检测器的设计

摘要:在通讯系统中,为了保证信息的可靠传输,一般需要在发送端加入固定的同步码组,而在接受断则需要检出该同步码组,保证信息的可靠接受,接收端的同步码检测器就是用来检测同步码组的电路,中间用到的码型检测电路部分实际上就是一个序列检测器,本文将采用VHDL硬件描述语言实现序列信号检测器的设计

关键词:序列检测,EDA,VHDL

毕业设计说明书目录

1 引言………………………………………………………………………11

2 方案简介…………………………………………………………………12

2.1方案一:……………………………………………………………12

用状态机设计一个序列检测器

2.2方案二:……………………………………………………………12

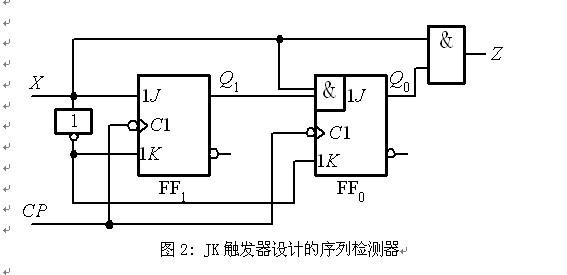

用JK触发器完成“1111”序列检测器的设计

3 各方案设计和论证………………………………………………………13

3.1 方案设计和论证……………………………………………………13

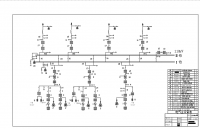

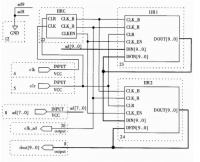

3.1.1方案一…………………………………………………………13

3.1.2方案二…………………………………………………………17

3.2方案比较……………………………………………………………21

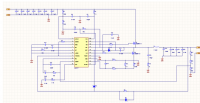

4软件设计…………………………………………………………………23

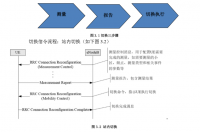

4.1程序流程…………………………………………………………23

4.2系统程序…………………………………………………………25

5系统调试…………………………………………………………………26

6参考文献…………………………………………………………………35

伴随着计算机,集成电路和电子系统的设计的发展,融合了计算数学,优化理论,图论和拓扑学等多学科精髓发展起来的电子设计自动化技术,正在成为现在电子设计技术的核心,EDA技术涉及面广,内容丰富,以其为技术的数字系统设计,已经具备完整的,成熟的设计方法和设计流程,为现代电子设计的进步和发展做出了巨大的贡献

在通讯系统中,为了保证信息的可靠传输,一般需要在发送端加入固定的同步码组,而在接受断则需要检出该同步码组,保证信息的可靠接受,,接收端的同步码检测器就是用来检测同步码组的电路,中间用到的码型检测电路部分实际上就是一个序列检测器,本文将采用VHDL硬件描述语言实现序列信号检测器的设计

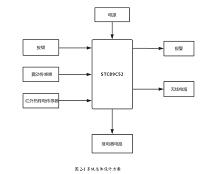

本论文以EDA的状态机为基础,在此基础上接受序列检测器电路。也包括了完整的控制电路和详细的原理说明;介绍了序列检测器的结构和工作原理以应用为目的。对一组信号传过来时,检测器就会对这组信号进行检测。如果检测出这组信号和原来设定的信号不符合,就会返回上一程序再进行检测,如果检测出这组信号和原来设定的信号是一样的,那就继续下一程序。

序列检测器是一种能把一组信号进行检测,并把显示结果显示出来的器件或装置。它具有灵敏度高,可靠性好,利于安装,误差小,并且具有低成本,适用性强等特点受到极大的欢迎。其次就是分析部分,如何在检测信息到来之后做到合理的分析并作到信息的反馈做出合理的处理

参考文献

(1)邓元庆,贾鹏 数字电路与系统设计。西安:西安电子科技大学出版社,2003

(2)康华光 电子技术基础。第四版。北京:高等教育出版社,1999

(3)任长明,刘锡海 数字系统逻辑设计技术,天津:天津大学出版社,1992

(4)江晓安,董秀峰,杨颂华。数字电子技术,西安:西安电子科技大学出版社,2002