基于EDA的序列检测器设计

摘要:文章通过设计序列检测器,介绍了利用ALTERA公司的Quartus II平台,通过硬件设计语言(VHDL),基于FPGA进行数字电路设计、描述、编译、仿真等主要流程,表明了运用EDA技术设计电路具有灵活性、可靠性和可扩展性,在硬件设计领域中必将得到很好的应用。

关键词: 电子设计自动化(EDA);FPGA/CPLD; Quartus II;硬件描述语言(VHDL)

随着电子技术的发展,数字系统的设计正朝着集成化、大规模和高速度方向发展。EDA(Electronic Design Automation,电子设计自动化)是以大规模可编程逻辑器件替代中小规模集成电路作为硬件载体,以EDA软件编程的方式对可编程器件进行电子系统设计的计算机辅助电路设计技术。目前已经广泛应用于电子电路与系统的设计和产品的开发,逐渐取代了传统的手工硬件电路设计方式。设计的系统具有体积小、重量轻、功耗小、速度快、价格低、可靠性高、设计周期短等优点。一个功能完备的EDA设计软件加上一片普通功能的可编程逻辑芯片就可以构成以前需几百个集成电路才能构成的电子系统。

EDA可以直接的面向用户需求,根据系统的行为与功能的要求,自顶向下地逐渐完成相应的描述,综合,优化,仿真,验证,最后生成器件。而传统的基于门级描述的电路随着规模的扩大与功能的复杂已经很困难完成设计的要求,HDL在这种情况下显示出了巨大的优势,它在硬件设计流域的地位就像C与C++在软件设计领域一样重要,而在大规模数字系统的设计中会更加受到青睐,并逐步的取代传统的逻辑状态图和逻辑电路图等硬件设计方法,成为主要的硬件描述工具。现在比较流行的HDL语言主要有两种:VHDL与Verilog HDL,这两种都成为IEEE的标准,各有其特点,但Verilog HDL比VHDL在代码的设计风格上更加简洁明了,灵活高效,更像C语言给编者更大的自由空间,在底层方面及开关级描述方面比VHDL有更加强大的功能,此外它还支持混合信号系统设计,相信它的应用前景会很不错。

Altera公司是著名的PLD生产商,多年来一直占据着行业的领先地位,该公司推出的CYCLONE系列FPGA内部的LPM可以实现微程序控制和管理复杂逻辑电路,它可以替代几十甚至几千块通用Ic芯片,具有处理速度快、存储容l 量大、I/0功能强、功耗低及实时响应快等特点,而且操作灵活,可以重复擦写无限次,扩展性强,FPGA技术已经成为数字IC设计中硬件与软件领域之间的一座桥梁。熟练地利用EDA软件进行PLD器件开发已经成为当代电子工程师必须掌握的基本技能。同时大规模和超大规模的可编程逻辑器件(PLD)不断推出,产品规模和性能也在迅速发展。基于查找表硬件结构的FPGA是当前进行快速系统原型设计最流行的ASIC手段。

Quartus II是Altera公司提供的FPGA/CPLD开发集成环境,是目前广泛使用的EDA软件之一,,它承接了MAX+PLUS II的全部设计功能和器件对象,增加许多新功能和新的FPGA器件系列,提供了功能全面的FPGA/CPLD集成开发工具,包括一些适用于SOPC开发的大规模器件。完整的多平台设计能满足各种特定设计的需要,其界面友好,使用便捷,易学易用、可视化等优点为业界所公认。

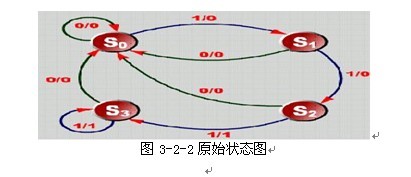

在通信系统中,为了保证信息的可靠传输,一般需要在发送端加入固定的同步码组,而在接受端则需要检出该同步码组,保证信息的可靠接收。接收端的同步码检测器就是用来检测同步码组的电路,中间用到的码型检测电路部分实际上就是一个序列信号检测器。序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,在数字通信中有着广泛的应用。本设计就是应用EDA知识设计一个序列检测器。

毕业设计说明书目录

1 引言………………………………………………………………………………………14

2 方案论证…………………………………………………………………………………15

2.1方案一:基于状态机的序列检测器的设计…………………………………………15

2.2方案二:基于数字电路的序列检测器的设计………………………………………15

3 方案设计和论证…………………………………………………………………………17

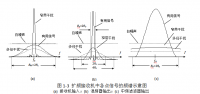

3. 1方案一:用状态机实现序列检测器………………………………………………17

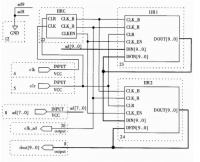

3. 2方案二:用JK触发器实现序列检测………………………………………………19

3. 3方案比较与选择……………………………………………………………………22

3. 3. 1状态机的基本设计思想………………………………………………………22

3. 3. 2有限状态机……………………………………………………………………23

3. 3. 3一般有限状态机的设计………………………………………………………24

4 软件设计…………………… …………………………………………………………25

4. 1程序流程…………………………………………………………………………25

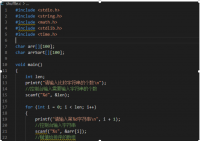

4. 2程序………………………………………………………………………………26

5 软硬件系统的调试………………………………………………………………………28

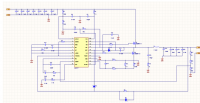

5. 1基于QuartusII软件的软件调试……………………………………………28

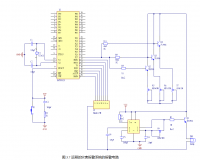

5. 2 基于FPGA 的硬件调试…………………………………………………………30

5. 3软硬件联调………………………………………………………………………31

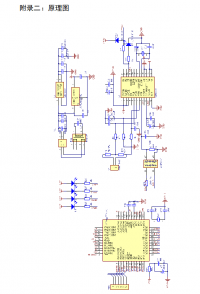

6 附录 ………………………………………………………………………………………32

7 参考文献 …………………………………………………………………………………33

参考文献

【1】潘松,黄继业,EDA技术与VHDL.第2版[⋯.北京:清华大学出版社,2007.

【2】高原,FPGA~l领设计工具走进ASIC领域[JJ。电子技术,2006,11

【3】赵倩,郭腊梅,闵敬国,嵌入式系统中高性能Mcu控制器的设计与实现[JJ.上海电力学院学报, 2006,22(2):109—112

【4】刘朝霞.基于VHDL的FPGA器件设计[J]微计算机信息,1998,14(6):80-82.

【5】范秋华,赵艳秋,何香玲.基于啪]L的彩灯控制[JJ.现代电子技术,2004,169(2):5-8

【6】程耀林.FPGA的系统设计方法解析[JJ.微电脑应用2007,23(1):48—50。基金项目:安徽高校省级自然科学研究重点项目资助(KJ2007A087)

【7】王长宏等.Verilog设计实例及仿真与综合[J].计算机应用,2001

【8】毛法尧.数字逻辑[M].jE京:高等教育出版社,2000

【9】夏字闻.Verilog数字系统设计教程[M].jE京航天航空大学出版社。2003

【10】杜建国.Verilog硬件描述语言[M].jE京:国防工业出版社。2004

【11】李德毅.数据挖掘研究现状 2000—11—16

【12】俞文彬,谢康林,张忠能.基于属性分类的数据挖掘方法[J],小型微型机算机系统,2000,21(3)

【13】范盟,孟小峰等译,Jiawei Hart,Micheline Kamber著.数据挖掘概念与技术[M].北京:机械工业出版社,2001

【14】刘刀桂,孟繁星编著.Visual C++实践与提高一数据库篇

【15】赵曙光,郭万有,杨颂华.可编程逻辑器件原理、开发与应用[M].西安西安电子科技大学出版社,2000.

【16】宋万杰,罗丰,吴顺君.CPLD技术及应用FM].西安:西安电子科技大学出版社,1999.