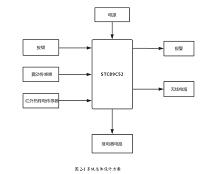

基于EDA技术的多功能频率计的设计 摘要:本文设计的等精度频率计主要由两大部件组成:CPLD可编程逻辑器件和单片机AT89C51。CPLD与单片机在电子系统设计中有很强的互补性,单片机能实现灵活的逻辑控制功能,具有很强的数据处理能力,而CPLD 拥有高速度、高可靠性,两者相结合可以取长补短,使设计达到硬件的最简化和软件的最佳化。这种组合将在电子系统的设计中发挥出越来越明显的作用。

关键词:等精度频率计 CPLD/FPGA VHDL 显示电路

1. 引言

随着科学技术与计算机应用的不断发展, 以单片机作为核心的测量控制系统层出不穷。在频率测量方面,被测信号中较多的是模拟和数字开关信号, 此外还经常遇到以频率为参数的测量信号, 例如流量、转速、晶体压力传感器以及经过参变量—频率转换后的信号等等。

对于这些以频率为参数的被测信号,通常多采用的是测频法或测周法:测频法是通过测量标准闸门时间内待测信号的脉冲数而计算出待测信号频率的,由于闸门时间通常不是待测信号周期的整数倍,因此存在最大±1 的待测信号脉冲误差,只能在信号频率较高时采用;而测周法是通过测量待测信号的周期并求其倒数而求得其频率的,在待测信号的一个周期内也存在最大±1 的标准信号脉冲误差,只能在信号频率较低时采用。

同时,对于频率变化较小的被测信号, 采用测频或测周法的效果很满意, 但当被测信号频率变化范围较大时, 比如100Hz~ 100kHz, 采用上述方法就很难满足在整个频率变化范围内都达到所要求的测量精度。

由此可见,测频法和测周法这两种频率测量方法都存在局限性,并难以实现宽频带、高精度测量。测频法和测周法只能对频率范围的两头频率实现较高精度的测量, 而对于中间频率或变化范围较大的频率, 不能同时都达到较高的测量精度。

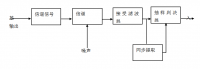

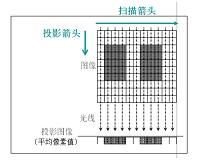

如果要求只使用一种测量方法而对频率变化范围较大的信号都能达到同样的精度, 就只能采用等精度频率测量技术。等精度频率测量技术又叫做多周期同步测量技术, 等精度频率测量仪器主要由被测信号计数器、参考信号计数器、同步闸门控制器、采样时间控制器以及运算单元等组成。

等精度测频的方法是:采用频率准确的高频信号作为标准频率信号,保证测量的闸门时间为被测信号的整数倍,并在闸门时间内同时对标准信号脉冲和被测信号脉冲进行计数,实现整个频率测量范围内的测量精度相等,当标准信号频率很高,闸门时间足够长时,可实现高精度的频率测量。 毕业设计说明书目录

1 引言……………………………………………………………………………………14

1.1 等精度频率计的背景 …………………………………………………………14

1.2 VHDL语言和Max+Plus II环境简介 …………………………………………15

2 方案论证………………………………………………………………………………16

2.1方案一 ………………………………………………………………………16

2.2方案二 ………………………………………………………………………17

2. 3方案三 ………………………………………………………………………17

2. 4方案的选择 …………………………………………………………………18

3.等精度频率计设计原理 ……………………………………………………………18

3.1频率的测量原理…………………………………………………………………18

3.2周期的测量原理…………………………………………………………………19

3.3脉宽的测量原理…………………………………………………………………20

3.4占空比的测量原理………………………………………………………………20

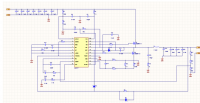

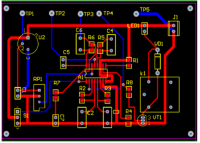

4. 硬件电路设计………………………………………………………………………20

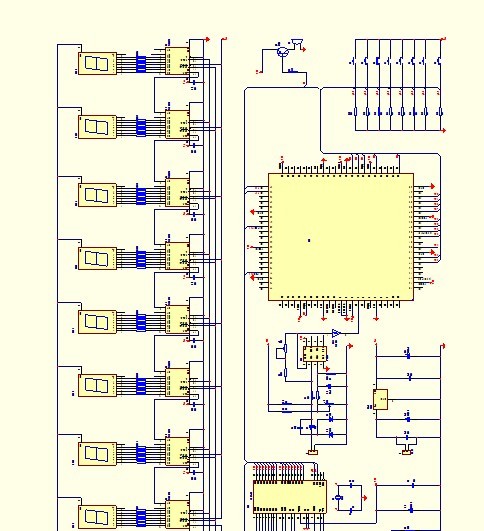

4.1可编辑逻辑器件(CPLD)简介…………………………………………………21

4.2AT89C51单片机简介……………………………………………………………22

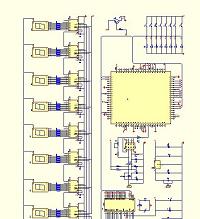

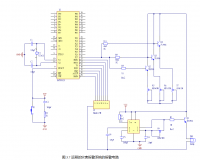

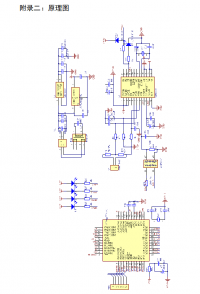

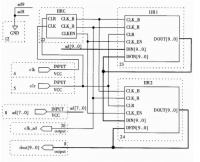

4.3等精度频率计各模块功能及电路图 …………………………………………23

5.软件设计……………………………………………………………………………27

5. 1 CPLD模块的软件设计………………………………………………………27

5.2 89C51程序流程 …………………………………………………………36

5.1.1系统主程序流程图………………………………………………………36

5.1.2各子程序流程图…………………………………………………………37

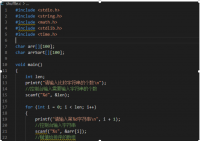

5.2程序 ……………………………………………………………………………42

5.1主程序 ……………………………………………………………………42

5.2各子程序 …………………………………………………………………44

6.软硬件系统的调试………………………………………………………………60

6.1软件调试 …………………………………………………………………60

6.2硬件调试 …………………………………………………………………60

6.3 仿真…………………………………………………………………………61

7. 附录 …………………………………………………………………………62

8.参考文献 …………………………………………………………………………64

参考文献

[1] 孙延鹏、张芝贤、尹常永.VHDL与可编程逻辑器件应用.北京:航空工业出版社,2006,23-34.

[2] 杨刚,龙海燕.现代电子技术——VHDL与数字系统设计.北京:电子工业出版社,2004,39-59.

[3] 蔡明生,黎福海,许文玉.电子设计.北京:高等教育出版社,2003,123-152.

[4] 曾繁泰,李冰,李晓林.EDA工程概论.北京:清华大学出版社,2002,,98-138.

[5] 于海雁,车速斌,李强.VHDL及其在数显频率计中的应.沈阳工业大学学报,2002.

[6] 张毅刚,彭喜源,谭晓昀.MCS - 51 单片机应用设计.哈尔滨:哈尔滨工业大学出版社,2006,138-187.

[7] 唐颖,阮文海.基于FPGA/CPLD芯片的数字频率计设计.浙江树人大学学报,2003.

[8] 张振,晋明武,王毅平.MCS-51单片机原理及应用技术.北京:人民邮电出版社,2000,167-243.

[9] 全国大学生电子设计竞赛组委会编,《全国大学生电子设计竞赛获奖作品精选(1994-1999)》.北京理工大学出版社,北京,2003,54-89.

[10] 宋万爪,罗平,吴顺君.CPLD技术及其应用.西安:西安电子科技大学出版社,2000年6月,78-103.

[11] 张毅刚,彭喜元,姜守达,乔立岩.《新编MCS-51单片机应用设计》哈尔滨工业大学出版社,哈尔滨.2003,25-126.

[12] 姜立东VHDL语言程序设计与应用.北京:北京邮电大学出版社.2001年8月第一版,23-34.

[13] 徐志军,徐光辉,李建中.大规模可编程逻辑器件及其应用.成都:电子科技大学出版社,2000,100-107.

[14] 潘松,王国栋编著.VHDL实用教程成都:电子科技大学出版社.2000年2月,80-103.

[15] 王道宪,贺名臣,刘伟.VHDL设计技术.北京:国防工业出版社,2003年8月第一版,3-9.

[16] 高书莉,罗朝霞.可编程逻辑技术及应用.北京:人民邮电出版社.2001年9月,12-25.

[17] 卢毅.VHDL与数字电路设计.2001年4月第一版,168-243.

[18] 任晓东、文博.CPLD/FPGA高级应用开发指南.北京:电子工业出版社,2003,22-29.

[19] Stefan Sjoholm,Lennart Lindh著.薛宏熙等译VHDL设计电子线路北京.清华大之4出版社,2000,65-83.

[20] PETER ALFKE.A 400MHz Frequency Counter.APPLICATION– FREQUENCY 6COUNTER,2002,23-32.

[21] 数字频率计CPLD设计.电子工程学,工学,论文中心.

[22] 黄继武,杨宏伟,明锋.单片机AT89C51在UHF和VHF频率测量系统中应用的研究.武汉大学学报,2004 ,第48卷第1期.

[23] 许军,傅苏黎,张奎山.依托EDA平台加速电工电子类课程教学改革,装甲兵工程学院学报.2005年第四期.

微信

QQ1:3097331788 QQ2:2601997959 QQ3:2993773635