0.5μm CMOS金属硅化物工艺技术研究

摘要: 金属硅化物广泛用于微电子器件中的源、漏、栅极与金属电极间的接触, 是制备纳米集成电路的关键材料之一。本文对不同硅化物薄膜的特性进行了分析并对适用于0.5微米CMOS 器件的各种自对准硅化物工艺进行了讨论。

关键词: 金属硅化物;薄膜;自对准;NiSi;工艺模块;

毕业设计说明书目录

摘要.............................................................................................................................1

引言.............................................................................................................................1

第1章 金属硅化物的基础知识............................................................................ 1

1.1 金属硅化物的概念..................................................................................... 2

1.2 金属硅化物的性质..................................................................................... 2

1.3 金属硅化物的应用......................................................................................2

第2章 金属硅化物的工艺特性............................................................................ 2

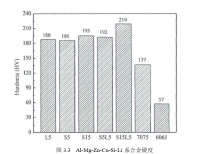

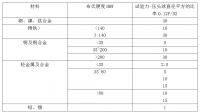

2.1 钛硅化物TiSi2............................................................................................ 5

2.2 钴硅化物CoSi2........................................................................................... 5

2.3 镍硅化物NiSi............................................................................................. 6

2.4 镍硅化物同钛,钴硅化物的比较..............................................................8

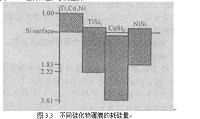

第3章 不同硅化物薄膜的电阻率....................................................................... 10

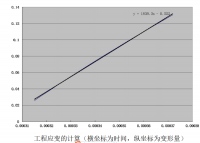

3.1 常规T iSi2 薄膜的方块电阻与线宽的关系............................................ 12

3.2 NiSi 薄膜的方块电阻与退火温度和线宽的关系................................. 12

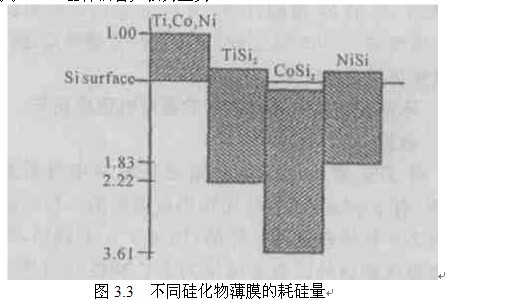

3.3 不同硅化物薄膜的耗硅量.........................................................................12

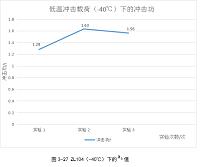

3.4. 不同硅化物薄膜的热稳定性....................................................................13

第4章 稀土金属硅化物........................................................................................14

第5章 自对准硅化物(Self-Aligned Salicides)技术....................................... 15

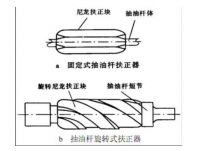

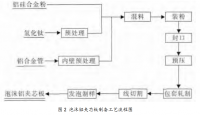

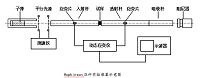

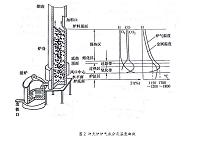

5.1 Salicide 工艺介绍......................................................................................16

5.2 工艺模块流程............................................................................................ 20

5.3 工艺模块控制要点.....................................................................................21

5.4 工艺模块结果............................................................................................ 21

5.5 自对准金属硅化物制备的可能问题点.....................................................23

第6章 金属硅化物的性能与缺陷监测评价....................................................... 25

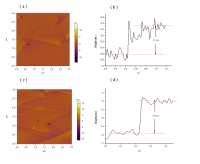

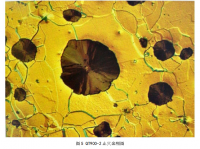

6.1 非晶界面层中的金属硅化物成核检测.................................................... 25

6.2 金属硅化物生成检测.................................................................................25

6.3 缺陷检测................................................................................................... 26

6.4 热稳定性分析........................................................................................... 26

第7章 结语........................................................................................................27

参考文献................................................................................................................28

在超大规模集成电路中, 随着电路规模的不断扩大和器件特征尺寸的不断减小, 互连线电阻对电路性能的影响变得愈发重要。重掺杂的多晶硅由于自身杂质固溶度的限制, 使电路的RC 延迟时间变长, 从而限制了特征尺寸的进一步减小。为了克服这一限制, 发展了低电阻率的难熔金属硅化物及其互连技术。金属硅化物最初应用到栅上有两种方法: 一种是将金属硅化物直接用作栅互连材料, 替代重掺杂多晶硅; 另一种是采用硅化物掺杂多晶硅复合栅结构(Po lycide) [1]。后者由于硅化物下面的多晶硅原子在高温氧化气氛中可以迅速穿过硅化物,并在其表面形成氧化层, 从而比较容易形成高质量的自钝化层, 以防止多晶硅中杂质的挥发; 并且, 硅化物掺杂多晶硅复合栅结构具有良好的工艺兼容性, 保持了多晶硅与二氧化硅之间良好的界面, 因而得到了广泛的研究。随着工艺技术的不断进步,1960 年代, 首次提出将硅化物用于硅接触孔, 以降低因接触孔尺寸变小、表面活性杂质浓度降低而导致的接触电阻的增加。在这种情况下, 硅化物采用金属与硅衬底热反应的方法生成。当器件尺寸进一步减小到深亚微米时,MOSFET [2]寄生串联电阻成为器件性能进一步提高的障碍。MOSFET 寄生串联电阻主要由接触电阻、薄层电阻、电流扩展电阻和电流积累电阻4 部分组成。为了同时克服源漏及多晶硅栅的接触电阻和薄层电阻对器件性能的影响, 硅化物自对准工艺应运而生。硅化物自对准工艺不仅同时降低了多晶硅和源漏区的薄层电阻和接触电阻, 提高了连线能力, 而且简化了工艺。

金属硅化物因具有良好的高温特性而广泛应用于电热元件和高温抗氧化涂层随着半导体集成电路临界线宽不断减小, 对金属电极的要求越来越高, 一方面其必须有高的导电特性, 另一方面又要耐高温, 并与硅有良好的界面接触。这类功能金属硅化物在大规模集成电路中主要用做源、漏和栅极与金属电极之间的接触。当前广泛使用的自对准硅化物工艺制程就是高速CMOS逻辑电路的关键技

术, 它能减小源/漏和栅电极的薄层电阻和接触电阻, 降低与栅极相关的RC延迟。金属硅化物在VLSI/ULSI器件技术[3]中起着非常重要的作用,被广泛应用于源漏极和硅栅极与金属之间的接触。其中自对准硅化物(self-aligned silicide)工艺已经成为近期的超高速CMO S逻辑大规模集成电路的关键制造工艺之一。它给高性能逻辑器件的制造提供了诸多好处。该工艺减小了源/漏电极和栅电极的薄膜电阻,降低了接触电阻,并缩短了与栅相关的RC延迟。另外,它采用自对准工艺,无须增加光刻和刻蚀步骤,因此允许通过增加电路封装密度来提高器件集成度。现在,金属硅化物的制备通常采用快速热处理工艺。快速热退火已经被证明在减少硅化物形成中的总热预算方面优于传统的加热炉技术。

参考文献

[1] James D. Plummer, Michael D. Deal, Peter B. Griffin, Silicon VLSI Technology Fundamentals, Practice and Modeling. 第一版,电子工业出版社,2003.

[2] 施敏.半导体器件物理与工艺[M].第二版.赵鹤鸣,等(译).苏州:苏州大学出版社,2004.

[3] 陈星弼,张庆中.晶体管原理与设计[M].成都:电子科技大学出版社,2004.256-258.

[4] Campbell S A.微电子制造科学原理与工程技术[M].第二版.曾莹,等(译).北京:电子工业出版社,2003.

[5] Marbell M N, Cherepko S V, Madiar A, et al. An improved large signal model for harmonic-balance simulation of Si LDMOSFETs[A]. 34th Europ Microw Conf [C]. Amsterdam, The Netherlands. 2004. 225-228.

[6] Tang C W, Tong K Y. A compact large signal model of LDMOS[J]. Sol Sta Electron, 2002,46(12):2111-2115.

[7] Aarts A C T, Kloosterman W J. Compact modeling of high voltage LDMOS devices including quasi-saturation[J]. IEEE Trans Elec Dev,2006,53(4):897-902.

[8] SU J, FANG J, WU J, et al. Characterization and modeling of a 700 V single crystal diffused LDMOS device[J]. Microelectronics,2004,34(2):192-194.

[9] Yang Y, Woo Y Y, Yi J, et al. A new empirical large singnal model of Si-LDMOSFETs for high power amplifier design[J]. IEEE Trans Microwave Theory and Techniques,2001,49(9):1626-1633.

[10] Wu X-L, Chen J-N, Ke D-M, et al. A circuit micro model of high voltage LDMOS based on numerical simulation [A]. IEEE Int Workshop VLSI Design & Video Tech [C]. Suzhou, China. 2005. 90-93.

[11] HE j, ZHANG X. Analytical model of surface field distribution and breakdown voltage for RESURF LDMOS transistors[J]. Chinese J Semicond , 2001, 22(9):1102-1106.

[12] Ameen M, Hebb J. Implanter, RTP system issues for ultrashallow junction formation[J]. Sol Sta Technol,2001,44(77):77-84.

[13] 陈曦,庄奕琪,杜磊:深亚微米CMOS集成电路抗热载流子效应设计[J].微电子学,2003,33(6):509-512.

[14] VASSILEV V, LORENZINI M, GROESENEKEN G. MOSFET ESD breakdown modeling and parameter extractions in advanced CMOS technologies[J].IEEE Trans Elec Dev, 2006, 53 (9): 2108-2117.

[15] MOHAN N, KUMAR A. Modeling ESD Protection[J]. Potentials IEEE,2005,24(1):21-24.

[16] ZHOU Y-Z, CONNERNEY D, CARROLL R, et al. Modeling MOS snapback for circuit-level ESD simulation using BSIM3 and VBIC models[C] // In: Proc Sixth Int Symp Qual Elec Des. San Jose, CA,UAS.2005:537-540.

[17] LEE J-W, LI Y-M. Effective electrostatic discharge protection circuit design using novel fully silicided NMOSFETS in sub-100-nm device era[J]. IEEE Trans Nanotechnol,2006,5(3):211-215.

[18] CHATTERJEE A, DUVVURY C, BANERJEE K. New physical insight and modeling of second breakdown (It2) phenomenon in advanced ESD protection device [C] // Int Elec Dev Meet. Washington DC,USA.2005:195-198.

[19] KER M-D, LIN K-H. Double snapback characteristics in high-voltage NMOSFETS and the impact to on-chip ESD protection design [J]. IEEE Elec Dev Lett,2004,25(9):640-642.

[20] JIAO C, YU Z-P. A robust novel technique for SPICE simulation of ESD snapback characteristic[C]//The 8th Int Conf Sol Sta and Integr Circ Technol.Shanghai,China.2006:121-124.

[21] Thompson S E, Armstrong M, Auth C, et al. A 90nm logic technology featuring strained-silicon[J].IEEE Trans Elec Dev,2004,51(11):1790-1979.

[22] Kim Y S, Mori T, Hayami Y, et al. A highly robust SiGe source drain technology realized by disposable sidewall spacer (DSW) for 65nm node and beyond [A]. Proc ESSDERC[C]. Washington D C,USA.2005.305-308.

[23] W.Lukaszek1, J. Shields, Electron Shading Effects During Oxide Etching in Uniform and Non-Uniform Plasmas, 7th International Symposium on Plasma- and Process-Induced Damage[DB/OL], Maui, Hawaii, 2002

[24] N.艾罗拉:用于VLSI模拟的小尺寸MOS器件模型(理论与实践)第一版,张兴,李映雪等译,科学出版社,1999.

[25] Giuseppe V. Power amplifiers for microwaves and RF applications with LDMOS transistors[J]. Microwave J, 2006, 40(6):98-102.

[26] B.Jzyant Baliga, “Power integrated circuits-a brief overview” IEEE Trans. Electron Devices, vol. ED-33, NO.12, December 1986.

[27] S.A.Buhler, D.L.Heald, R.R.Ronen, T. Gannon and P.Elkins, “Integrated high-voltage/low-voltage MOS devices” IEDM Technical Digest, pp.259-262,1981.

[28] P. R.Gray and R.G.Meyer, Analysis and Design of Analog Integrated Circuits, John Wiley and Sons, Inc: New York, 1993.

[29] Y.P. Tsividis, Mixed Analog-Digital VLSI Devices and Technology, McGraw-Hill: New York,1996.

[30] P.Tsui, P.Gilbert, and S.Sun, “Integration of power LDMOS into a low-voltage 0.5um BiCMOS technology,” IEDM Technical. Digest, pp.27-30,1992.

[31] Ed. Wai-Kai Chen,“The VLSI Handbook”, Boca Raton, CRC Press LLC, 2000.

[32] P. M. Santos, A.P. Casimiro, M. Lança and M. I. Castro Simas, “High-Voltage Solutions in Standard CMOS Technology”, Microelectronics Journal, Vol. 33, pp. 609-617, 2002.

[33] J. A. Herrera1, J. L. Del Valle, “900 MHz band class E PA using high voltage n-channel transistors in standard CMOS technology”, 2nd International Conference on Electrical and Electronics Engineering (ICEEE) and XI Conference on Electrical Engineering (CIE 2005), September 7-9, 2005

[34] H. Ballan and M. Declercq, “High Voltage Devices and Circuits in Standard CMOS Technologies”, Netherland: Kluwer Academic Publishers, 1999.

[35] 朱炜玲 等 热载流子效应对n-MOSFETs可靠性的影响 华南理工大学学报 2003 31(7)33-36

[36] J. Park, B. Lee, D. Kim, C. Yu, and H. Yu,“RF Performance Degradation in NMOS Transistors due to Hot Carrier Effects”, IEEE Transactions on Electron Devices, vol. 147, no. 5, pp.1068, May 2000

[37] 杨谟华,方朋.”VLSI/ULSI可靠性的监测与模拟,” 电子科技导报,1998,(12):19-23.

[38] Hirokazu Yonezuqa,Jingkun Fang,Yoshiyuki Kawakami,etc.Ratio based Hot-Carrier Degradation Modeling for Aged Timeing Simulation of Millions of Transistors Digital Circuits, IEDM Technical digest,pp:93-96,1998.

[39] BTA Technology,INC.,BTABERT Users Manual,1997.

[40] M. Saxena, S. Haldar, M. Gupta, and R.Gupta, “Physics-Based Analytical Modeling of Potential and Electrical Field Distribution in Dual Material Gate (DMG)-MOSFET for Improved Hot Electron Effect and Carrier Transport Efficiency”, IEEE Transactions on Electron Devices, vol. 49, no. 11, pp.1928, Nov 2002

[41] SILVACO International, Santa Clara, Athena User’s Manual, February 2000

[42] W.Lukasezek, Wafer Charging Damage in IC Process Equipment[DB/OL], ECS International Semiconductor Technology Conference, Shanghai, China, 2001.

[43] K.P.Cheung,Plasma Charging Damage[M], Great Britain, Springer, 2001.

[44] 刘之景.等离子体刻蚀加工中的器件损伤[J],仪表技术与传感器,1999(5):13-14.

[45] 赵毅,徐向明.MOS器件中的等离子体损伤[J],半导体技术,2004(8):34-37.

[46] 唐瑜,等.等离子体对90nm 工艺MOS 器件的损伤[J],半导体学报,2007(1):92-95.

[47] 朱志炜,等.等离子体工艺引起的MOSFET 栅氧化层损伤[J],固体电子学研究与进展,2003(1):126-132.

[48] 刘之景,曹继,王克逸.超薄氧化门的等离子体充电损伤机理[J],半导体技术,2002(3):63-66.

[49] 胡恒升,张敏.等离子体充电效应在薄氧化硅层产生陷阱密度的确定[J],功能材料与器件学报,2001(1):59-62.

[49] 于宗光,叶建民,王成:亚微米门阵列ASIC设计技术,电子与封装,2005,22(2):36-42.