基于CPLD的信号发生器的设计与实现

摘 要

数字信号指幅度的取值是离散的,幅值表示被限制在有限个数值之内。二进制码就是一种数字信号。二进制码受噪声的影响小,易于有数字电路进行处理,所以数字信号发生器广泛应用于电子工程、通信工程、自动控制、遥测控制、测量仪器、仪表和计算机等技术领域。常用的数字信号发生器产生的波形单一且移植性差,所以本文采用Quartus Ⅱ开发平台,基于可编程逻辑器件CPLD设计出方波、脉冲波、m序列、正弦波的数字信号,。整个设计采用Verilog HDL编程实现,其设计过程简单,极易修改,可移植性强。CPLD还具有可编程重置特性,因而可以方便地更换波形数据,且简单异行。

关键词:CPLD,Verilog HDL,Quartus Ⅱ,数字信号发生器

ABSTRACT

Digital signal to amplitude values are discrete, amplitude that is restricted within a limited numerical. Binary code is a kind of digital signal. Binary code under the influence of the noise is small, easy to have the digital circuit for processing, so the digital signal generator is widely applied to the technical field of electronic engineering, communication engineering, automatic control, remote control, measuring instruments, instrument and computer. Digital signal generator used in the waveform of single and poor portability, so this paper uses Quartus development platform, the CPLD programmable logic device designed with periodic and aperiodic signal based on. This design uses Verilog HDL programming, the design process is simple, easy to modify, portability strong. CPLD also has a programmable reset properties, which can replace the waveform data, and simple line.

Keywords: CPLD, Verilog, HDL, Quartus Ⅱ, digital signal generator

目 录

1 绪论 1

1.1 CPLD 1

1.2 Verilog HDL 5

1.3本文框架及研究内容 5

1.4 本章小结 6

2 信号发生器技术 7

2.1信号发生器原理 7

2.2信号发生器的用途 7

2.3信号发生器的分类介绍 8

2.4本章小结 10

3 数字信号发生器的设计 11

3.1 总体设计 11

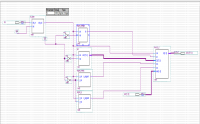

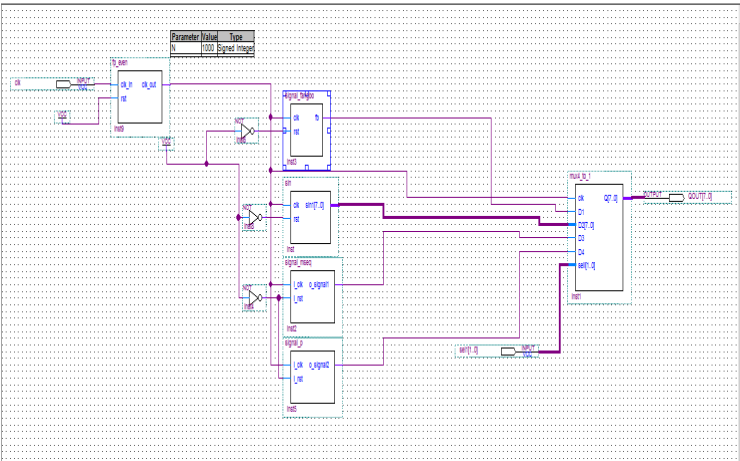

3.2 顶层模块设计 11

3.3方波的设计 12

3.4脉冲波的设计 13

3.5 m序列的设计 13

3.6正弦波的设计 15

3.7 本章小结 16

4 测试验证 17

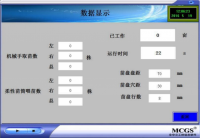

4.1 quartus上的仿真测试 17

4.2 信号输出测试 18

4.3 本章小节 21

5 结论与展望 22

5.1 结论 22

5.2 展望 22

参考文献 25

致 谢 26

附录 27

1 绪论

在电子技术领域,常常需要波形、频率、幅度都可调的电信号,用于产生这种电信号的电子仪器称作数字信号发生器。

信号发生器是一种常用的信号源,广泛运用于科学研究、生产实践和教学试验等领域。特别是在通信系统的科研实验中,常常需要用到不同频率和幅度的信号,如正弦波、方波、脉冲波、m序列等。作为一种为电子测量和计量提供电信号的设备,它和万用表、示波器、频率计等仪器一样,是最普通、最基本,运用最广泛的电子仪器之一[1]。

传统的波形发生器受到很多独立的模拟原件的约束,不能够产生种类很多的波形,由于它的体积大、灵活性和稳定性相对比较差[2]。这些年来,用CPLD和FPGA这些可编程逻辑器件来产生数字信号发生器变的越来越流行,因为这些可编程逻辑器件具有很快的运行速度,可以现场编程直接输出想要产生的波形,相对与那些固定的信号发生器,可编程逻辑器件生成的信号发生器还可以节约成本。

正是基于这样的需求,本文详细讨论了怎么样基于CPLD完成一个数字信号发生器的设计。该设计采用Quartus Ⅱ软件作为平台,Verilog HDL语言作为开发语言,基于CPLD配合相应外围电路实现一个数字信号发生器,其电路结构简单,容易扩展,具有极大的灵活性和方便性,实现了产生矩形波、脉冲波、正弦波、m序列的数字信号发生器。

1.1 CPLD

1.1.1 CPLD概述

复杂可编程逻辑器件是伴随着半导体技术的不断提高,发展到能够满足大部分用户的需求,而且它的集成密度在不断的提高[3]。现在已经有许多种类的CPLD器件,它们具有不同的特点,但大体上还是相同的,相同的地方包括三部分:逻辑阵列块是二维的,构成逻辑的核心器件是一样的,输入和输出模块连接的都是互连资源的逻辑块。

现在有一百万个门级的CPLD芯片系列,随着工艺水平的提高,在同时增加器件的容量时,以提高使用CPLD器件的速度和频率为目标,它进行了许多内部结构的改进,各种不同形式的内部结构开始出现,功能变得更齐全,扩展应用变得更多。

1.1.2 CPLD与FPGA的比较

由于各PLD公司的CPLD/FPGA产品在价格、性能、逻辑规模和封装等方面各有千秋,不同的开发项目必须做出最佳的选择[4]。在应用开发中一般应考虑器件的逻辑资源、芯片速度、器件功耗的选择,这些很大程度上都会对设计有着决定性的作用。有时候选择了不适合的器件,往往就会对设计造成很大的麻烦。

CPLD和FPGA还有一个区别,对于大规模的逻辑设计,一般都是选择FPGA,因为FPGA的逻辑门数从5000到2000000门,基本上适合大规模的的逻辑设计。CPLD下电之后,之前烧入的逻辑结构是不会消失的[5]。但是FPGA下电之后,我们却要重新加载逻辑结构,这大大耗费了时间和资源。我们将以乘积项结构方式构成逻辑行为的器件称为CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列、Altera的MAX7000S系列和Lattice(原Vantis)的Mach系列等。将以查表法结构方式构成逻辑行为的器件称为FPGA,如Xilinx的SPARTAN系列、Altera的FLEX10K或ACEX1K系列等。

尽管FPGA和CPLD都是可编程ASIC器件,但由于CPLD和FPGA结构上的差异,它们的特点却不相同:

(1)当我们用到算法以及组合逻辑多的时候,我们选用CPLD,当我们用的是以时序逻辑电路为主的时候,我们用FPGA。换句话说,FPGA用到的是触发器丰富的结构,而CPLD用到的是触发器乘积项丰富的结构。

(2)CPLD的时序延迟比较均匀,而FPGA的误差很大,所以CPLD的延迟是可以预测的,而FPGA的延迟是不可预测的[6]。

(3)FPGA的灵活性比CPLD要大,取决与FPGA的结构,因为FPGA的内部连线是可以改变的,而CPLD只能通过它本身固定的内部连续去编程。CPLD的编程是在逻辑模块下进行的,而FPGA是对内部连续的改变来实现编程。

(4)它们的集成密度不同,CPLD的集成密度高,而FPGA的布线结构和逻辑结构却比CPLD复杂[7]。

(5)FPGA比CPLD使用起来复杂一点,因为CPLD编程采用E2PROM和FASTFLASH技术,它自身就可以存储编程信息。而FPGA的编程信息需存放在外部存储器上,相对于CPLD较为复杂一点。

(6)FPGA的速度比CPLD的慢,它的时间可预测性很比CPLD小。这是由于它们的结构导致的,FPGA的门级编程和分布式互联要比CPLD的互联集总式的逻辑块编程复杂的多。

(7)CPLD的保密性比FPGA的好[8]。

(8)集成程度越高,FPGA的功耗却比CPLD要小的多。

1.1.3 CPLD的基本特点

(1)采用CPLD设计ASIC电路,布线延迟固定,它的时序稳定。

(2)CPLD可以作为中试样片设计ASIC电路[9]。

(3)CPLD内部的触发器比较多,I/O引脚丰富。

(4)CPLD在ASIC电路中的设计周期比其它器件都要短,而且资源比较省。

(5)CPLD编程数据不会丢失,电路简单[10]。

全球知名的CPLD生产厂商有:

(1)Altera,开发平台是Quartus II

(2)Xilinx 开发平台是ISE

(3)Actel ,开发平台是Libero

(4)Lattice

(5)Atmel

Altera公司的产品分为两大系列,MAX系列和FLEX系列[11]。MAX系列采用可编程的与阵列和固定或阵列实现逻辑功能,采用ERROM工艺或EEPPOM工艺[12]。FLEX系列是灵活的逻辑单元阵列,内部结构使用查找表实现逻辑功能,使用SRAM工艺。所有Altera器件系列都使用CMOS处理工艺,它比双极性工艺具有更低的功耗和更高的可靠性。

参考文献

[1]刘泉,阙大顺,数字信号处理原理与实现,电子工业出版社,2005.

[2]李哲英,骆丽,数字集成电路设计,机械工业出版社,2007.

[3]徐志军,尹廷辉,EDA技术与VHDL设计,电子工业出版社,2009.

[4]高泽溪,高成,直接数字频率合成器(DDS)及其性能分析,北京航空航天大学学报,1998

[5]王志鹏,付玉琴.可编程逻辑器件开发技术MAX+plus II.北京:国防工业出版.

[6]张鑫,华臻,陈书谦,单片机原理及应用[M],电子工业出版社,2005.

[7]赵佩华,眭碧霞,单片机原理及接口技术[M],机械工业出版社,2008.

[8]邹振春,MCS-51系列单片机原理及接口技术[M],北京:机械工业出版社,1999.

[9]刘爱荣,王振成,EDA技术与CPLD/FPGA开发应用简明教程,清华大学出版社,2007.

[10]梁勇,王留奎,EDA技术教程,人民电邮出版社,2010.

[11]楼然苗,51系列单片机设计实例[M],北京:北京航空天大学出版社,2003.

[12]徐志军,徐光辉,CPLD/FPGA的开发与应用,电子工业出版社,2002.

[13]王丹利,王丽英,CPLD/FPGA可编程逻辑器件实用教程,机械工业出版社,2006.

[14]王建校,电子系统设计与实践[M],高等教育出版社,2008.

[15]陈伟人,单片微型计算机原理与应用[M],北京:清华大学出版社,2006.

[16]夏宇闻,复杂数字电路与系统的Verilog HDL设计.北京:北京航空航天大学出版

[17]夏宇闻,Verilog-HDL数字系统设计教程,北京航空航天大学出版社,2003.

[18]汪国强,EDA技术与应用,电子工业出版社,2006.

[19]Mark Zwolinski. Digital System Design with VHDL. 北京:电子工业出版社,2002.

[20]L.J.Kuslmer,The composite DDS-A new direct digitals synthesizer architecture,IEEE Proc,47th AFCS,1993.