使用现场可编程门阵列进行电路设计

各种定制逻辑

在多数数字设计中,可按如下类别对电路进行分类。

标准产品:该类产品提供的功能并不如特定应用领域相联系,很宽范围内的器件提供的功能都是相同的。该类产品的典型器件有微处理器和存储器。

专用标准产品:该类产品提供的功能并不如特定实现相关,对于某种应用领域提供的功能是相同的。该类产品的典型器件有MPEG解码器。

定制逻辑:该类逻辑和特定应用相关,这是不同产品相互区分的关键所在。该类产品通常是互联逻辑,将标准产品和专用标准产品相互连接起来。

定制逻辑的实现方法有多种选择,现场可编程门阵列是其中之一。下面对这些技术进行讨论。

专用集成电路

ASIC就是专用集成电路的缩写。它是一种为满足特定应用需求而定制的集成电路。今天的专用集成电路通常用“标准单元”方法来设计。这就是说,电路并不在晶体管层次进行设计,而是在门电路,触发器和存储模块的级别进行设计的。该方法的基础是一个由半导体制造商提供的基本元件库。专用集成电路有如下特点:生产成本极低,设计密度极高,开发难度极大。

门阵列

门阵列提供生产商定义的大量固定门电路结构和可以根据应用需求定制的互联电路。门阵列有如下特点:生产成本低,设计密度低,开发难度大。

现场可编程门阵列

FPGA是现场可编程门阵列的缩写。这个词是指一种可以在现场(即由系统制造商)编程的集成电路。FPGA有如下特点:生产成本高,设计密度低,开发难度低。

FPGA的用途

过去FPGA占有的市场份额很小。其典型应用为原型系统和仿真系统。用FPGA实现真正的产品,其复杂度过低;而将FPGA用于中等规模生产,其价格又过高。过去几年中,FPGA技术有了长足的进步,极大的改变了FPGA的应用方式。

FPGA正用于主流产品中(网络,电信,数字信号处理,消费类电子产品)

FPGA设计多于ASIC设计

实例研究

仅仅几年前,FPGA还只是应用在半导体行业中某些重要的边缘领域。因为其

灵活性,FPGA广泛用于ASIC仿真,互连逻辑集成,或者用做功能繁多,标准不断变化的应用解决方案之一。通常情况下,FPGA的生产工艺技术至少要滞后业界现有水平一代,而重复编程能力是由量产价格,内部性能和开发工具的编译速度决定的。

今天,FPGA往往是系统的核心。它不仅生产量大,技术先进,而且还进入了半导体产品的主流。市场的开拓,技术的创新,成本的构成以及开发工具的使用,无一不深受亚微米时代的影响。所有这些因素使FPGA成为一种替代ASIC设计的可行方案。由于FPGA功能灵活,上市时间快,所有被用作各种产品(网络产品,工业产品,消费类产品)的生产方案。在结构上,FPGA通过设计可以最大程度地减少亚微米技术存在的普遍问题,而这些问题在ASIC抽象中存在。在跟随整个半导体行业发展的过程中,业界领军的各大FPGA公司不断获得发展动力,而中小公司联合起来,或者寻求专用领域进行开发。

哪些因素在推动着FPGA技术的普及,以至于FPGA在许多应用中正在替代门阵列和标准单元ASIC?关键因素有如下几点:产品周期的缩短,对更高集成度(门阵列无法实现的)的需求,向深亚微米工艺技术的快速转移和网络应用的急剧扩张。

机顶盒 重复编程能力是一种动力,它允许设计人员在研发阶段大胆地探索,创新,而不丢失上市时机。重复编程能力也能荣许标准的不断变化和上市前的设计修改,它使真正的“在系统可配置”得以实现。这样,电信开发商使用一片芯片就可以实现多种应用,而不是每个特定需求都要使用一片ASIC。机顶盒就是这样一个例子:机顶盒制造商发现一片FPGA能够替代3片ASIC,而每片ASIC分别服务于亚洲,欧洲和北美洲各自的技术规格。

FPGA供应商的知识产权核(IP)正在逐步包含关键的系统级内核(PCI,DSP,微处理器接口)和关键的电信应用内核。设计人员可以将这些内核直接植入设计当中,这样做既不必重新创建内核设计,又可以缩短产品的上市时间。在生产中,设计人员越来越多地使用FPGA。虽然原因格不相同,但都和逻辑产业正在发生的变化相关。

光纤信道切换 光纤信道切换是一个例子。设计人员选择FPGA来实现某个光纤信道切换的工程项目,这是因为其ASIC计划无法在一个合理的时间内实现。这个光纤信道系统旨在将宽带从200Mb/s提高到满足IBM协议的1Gb/s。该系统必须允许复用和解复用向更高宽带的平滑过渡。起初,打算使用FPGA做出整个系统的样机;一旦试生产转为量产,然后就转向设计ASIC。

因为出现了错误,所以ASIC设计又回到了构造阶段;与此同时,FPGA价格在持续下降。由于资源有限,设计人员选择进入产品开发阶段,而不是继续设计,降低成本。他们也不愿意放弃可编程的好处。

专用集成电路和现场可编程门阵列

设计高性能的全定制集成电路当然是一件非常困难的工作。在全定制集成电路设计中,任何事情一直到包括每个晶体管可能都需要设计(尽管可以使用元件库)。然而,用门阵列制造半定制集成电路已有多年。顾名思义,门阵列是一种集成了逻辑门阵列的集成电路。所以,使用门阵列设计专用集成电路需要定义阵列中门之间的连接方式。从现实角度看,这意味着需要设计一层或二层金属互连线。制造集成电路的工艺流程分为七个或更多的阶段,除最终金属化阶段外的其他阶段都可提前完成,由于门阵列可以大批量生产,所以每个器件的成本就比较低。

ASIC一词通常来指全定制和半定制集成电路。可编程逻辑是另一类集成电路。最早的可编程逻辑器件(PLDs)是可编程逻辑阵列(PLAs)。与门阵列一样,可编程逻辑阵列是由功能待定逻辑组成的阵列;它和掩模可编程逻辑阵列的区别在于:可以用一个大电压(极性通常为负)决定阵列的配置。有些PLAs是电可编程的,也可以使用紫外线照射进行编程。可编程阵列逻辑(PALs)扩展了PALs,它包含12个触发器。近年来,可编程器件变得更加复杂了,复杂可编程逻辑器件(CPLDs)和现场可编程门阵列(FPGAs)就是其中的两种。

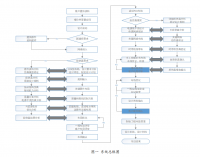

设计流程

大多数数字系统是时序的。也就是说,系统中有许多状态,而输出依赖于当前的状态。某些早期的计算机设计不是同步的。换句话说,输入一稳定下来就向新的状态转移。数字系统的同步设计倾向已经有多年了。在一个同步系统中,状态的改变是由一个或多个时钟信号触发的。为了设计稳定的系统,人们定义了规范的设计方法。用分立门电路设计(同步时序)数字系统,可按照如下步骤进行。

1.写出设计规格。

2.如果需要的话,将设计分解为若干个小部分,并为每一部分写出设计规格。

3.根据设计规格,画出状态机转换图。该图包括系统的每一个状态,引起状态变化的输入条件和每个状态的输出。

4.将状态数最小化。这是一个可选步骤,并不是在所有情况下都有用。

5.为每个状态分配布尔变量。

6.推导出次态逻辑和输出逻辑。

7.对次态逻辑和输出逻辑进行优化,从而将所需的门数量减至最小。

8.为逻辑门选择合适的布局——集成电路中包含哪些逻辑门以及各个集成电路在印刷电路板上的位置。

9.设计集成电路之间的走线。

一般而言,步骤1和步骤2是不能忽略的。因为这里需要设计者创造性的工作。大多数数字设计的书籍集中讨论步骤3~步骤7。步骤8和步骤9可以手工完成,但元件布局和布线是最早成功实现自动化的设计任务之一。如果将设计转换成计算机可读的形式,那么就可能在设计的不同阶段进行仿真。为了进行布局和布线,在步骤7中一般使用原理图输入程序;这样,就可以输入电路的门级结构了。可以把原理图转换成为适合逻辑仿真的形式。在步骤9完成之后,电路的结构(包括互连线的电阻和电容引起的延迟)可以提取出来,然后进行再次仿真。

因此,在专用集成电路和现场可编程门阵列上实现数字设计,需要配置预定义逻辑模块之间的连接。正像刚才提到的,我们不能够忽略步骤1和步骤2,步骤8和步骤9可以自动完成。使用HDL意味着可以将设计输入到CAD系统中,并可以在步骤3和步骤4进行仿真,而不仅在步骤7.所谓的“寄存器传输级”综合工具可以自动化完成步骤6和步骤7。步骤4仍需手工完成。步骤5可以自动完成,而可以迅速对某种特定状态分配的结果做出评估。行为综合工具开始出现在自动化设计中的步骤2附件。