半导体器件在线性应用

20世纪无疑是电子技术的世纪,当然,许多其他行业如医药、交通、科学、商业等也取得很多进步,但如果没有电子技术所提供的仪器和设备这些行业能取得这么大的进步吗?

我们最熟悉的数字系统是以10为基即十进制系统。但近年来科技的发展却需要产生其它的数字系统,如电子计算机需要开发可以适应电子处理的数字系统,这些数字系统是二进制(基为2),八进制(基为8)和十六进制(基为16)。

二进制系统是计算机的基本语言,而八进制和十六进制系统通常在计算机通信和计算机储存信息时用。因为计算机只能处理二进制数据或其它系统如八进制和十六进制中的二进制编码,所以十进制系统必须先转换成这些系统才能用计算机进行处理。当计算机对所给的信息处理完毕后,输出的信息是以非十进制形式打印或显示出来,因此这些输出信息也必须再转换,这次是转换回十进制系统。

数字电子技术是一门逻辑科学,一般来说,逻辑学是按一般原则进行推理的科学。数字逻辑学是用数字推理的科学。几乎所有的数字(逻辑)功能都可以用一种特殊的称为门的电路来实现。如果逻辑运算太复杂,无法用一个门来实现,也可以通过几个门的组合来实现这个逻辑运算。这些扩展的逻辑电路被称为组合逻辑电路。

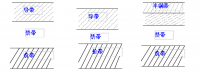

两种最基本的逻辑函数是“与”和“与非”函数,这两个函数的差别在于它们是互补的,即在功能上是相反的。“与”门的数字逻辑功能是当它所有的输入为高电平时它的输出为高电平。图8.1(a)给出一个“与”门的符号,它有二个输入端A、B和一个输出端C。门电路最多可以有8个输入端。

当“与”门的二个输入(或当它的输入不止两个时,所有的输入)为高电平(1)时它输出高电(1)。这个关系通常可以写作:C =AB这个表达式可以说成:当A等于1且B等于1时有C等于1或A与B等于C。

“与非门”比“与”门用得更普遍(图8.1(b)),它和“与”门是互补的,即逻辑上它的输出和“与”门相反。因为“与非”门的电路实现比较简单,所以它比“与”门便宜,使用也方便。在AND前面的字母N意味着是非“与”。逻辑(表达式)中对一个非门也有不同的表示法,常用字母上加一个上划线来表示非的关系。它表示“A与B等于非C”。在与非门中,大部分情况下它输出都为高(1),除非当所有的输入都为高时,与非门的输出为低(0)。

“或”门(图8.1(c))的逻辑功能是指当“或”门的任何一个输入为逻辑上高电平(1)时它输出为高(1),这种逻辑功能通常可写成:

C=A+B加号(+)”意味着“或”这种逻辑关系,可说成:“如果A或B等于1则C等于1”。

单个逻辑门是构造块,如果只需要一个单一逻辑关系时可以只用它们其中一个,但要实现更复杂的逻辑运算时它们也可以与其它门结合构成组合逻辑门。有时用一种门去代替其它的门更有利,设计者可以用手边的门电路来实现各种电路,这就是数字集成门电路的多功能性和适应性。

微处理器要用到锁存器和触发器,通过在RS锁存电路的输入端加一对“与非”门,可以达到两个目的:一是不用反相输入,二是两个“与非”门有一个公共输入端。这个公共输入端可以使这个电路与其它同类电路同步,这就是图8.2(a)所示的可控RS“与非”门锁存器。

R和S的输入端通常接逻辑0(低电平),要改变锁存器的输出状态,R或S必须输入高电平1。但是还要考虑一个新因素即第三个输入端。这个输入端一般标为C或CLK,因为它是由某种时钟电路控制的,起到控制若干个这样的锁存器同步工作的作用,只有当CLK输入是逻辑1时输出才可能改变,当CLK是逻辑0时,S和R端的输入不起作用。

要遵守不能同时在S和R输入端加信号(即同时为高电平)的规则,如果时钟端为逻辑1时在S和R输入端都为1,锁存器导通,两个输出均为逻辑1,这时如果CLK输入先降为逻辑0,毫无疑问,出现一种竞争的情况,将无法确定输出端Q和 中哪一个输出为逻辑0,8.2(a)中的电路表现出这种不确定性。

边缘触发的RS触发器实际上由两个同样的RS锁存电路组成,RS触发器的电路符号如图8.2(b)所示。在两个时钟输入之间接了一个反相器以保证这两个部分(RS锁存电路)分别在时钟信号的不同半周期中工作(即一个在时钟信号为高电平时工作,另一个则在时钟信号为低电平时工作)这就是这个电路的关键。 所以,Q和输出只能在时钟信号从1降到0时即时钟信号的下降沿发生改变。因此就称为边缘触发的触发器。

JK触发器在各种情况下的输出都是完全确定的,因此对大部分逻辑电路设计来说选择JK触发器比较好。一个JK触发器的Q和输出只在CLK信号的下降沿时改变状态, 这时J和K的输入状态将决定JK触发器的输出状态。

如果J和K输入端(图8.2(c))保持逻辑1(高电平),而时钟信号不断地交变时,Q和输出将在CLK的每个下降沿发生改变。这一特点在许多地方都很有用。一个专门以这种方式工作的触发器(J与K连接在一起)用T表示,构成T触发器。这种方式工作的JK触发器必须是边缘触发式的,任何高电平触发式的JK锁存电路如果三个输入端均为逻辑1时会高速振荡,这种电路是没什么用的。同样,T触发器也必须是边缘触发式的,边缘触发是保证这两种触发器每来一个时钟脉冲仅改变一次输出状态的唯一方法。

D触发器(图8.2(d))也是当时钟脉冲从逻辑1降到逻辑0时可能改变输出状态,且Q端的输出总是与在时钟下降沿时D的输入状态一致。这一点与RS和JK触发器不同的。

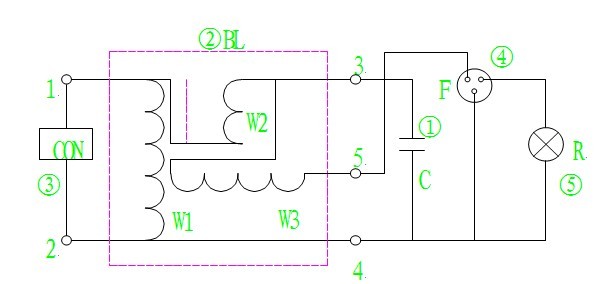

这个课程模块介绍了半导体器件在线性应用范围中的特征,内容包括半导体二极管: PN结二极管,特殊二极管;三极管:场效应三极管,晶体三极管;信号放大电路:实际放大电路,偏置电路、运算放大器电路;其它电路:整流,稳压,直流电压源电路。

这个单元学习以下的内容:逻辑电路的基本概念,数字表示方法,组合逻辑电路,时序逻辑电路,CMOS数字电路,逻辑运算定律和布尔代数,数字运算(二进制,十六进制,整数)组合逻辑电路的分析与综合,时序逻辑电路的分析与综合,寄存器,计数器,总线系统以及逻辑电路设计中的计算机辅助设计工具(软件)。

在电子电路的学习中基本且重要的电路(器件)是理想电压放大器。一般来说,理想电压放大器有二个输入端,v1 和 v2,和一个输出端vo,输入和输出之间的关系由vo=A(v1-v2),其中A称为放大器的增益。

注意到因为理想运算放大器的输入阻抗R=∞,当这个放大器连接到任何电路中,都没有电流流入(运放的)输入端,还有因为输出电压Vo是一个理想电压源两端的电压,为了简单化,不管输出端接什么器件,有vo=A(v1-v2)