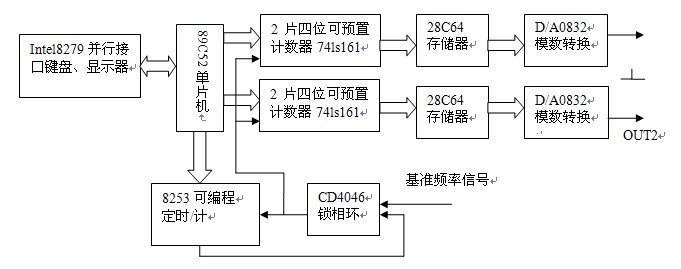

微机接口技术与芯片多处理技术的设计

微机接口

微机接口实现两种信息形式的交换。在计算机之外,由电子系统所处理的信息以一种物理信号形式存在,但在程序中,它是用数字表示的。任一接口的功能都可分为以某种形式进行数据库变换的一些操作,所以外部和内部形式的转换是由许多步骤完成的。

输入/输出单元将数字“开/关”电压信号转换成能通过系统总线传送到计算机的信号形式。这里每一根线的状态,无论是“开”或是“关”,用相应的“1”或“0”表示。对于已经转换成数字形式的模拟输入量,内部表示中用1和0组成的排列形式与被转换量相对应的二进制数。

从接口得到的愿数值会受到接口电路设计的限制,而且常需要线性化和量程调整才能形成适合于在主程序中使用的数值。举例来说,接口可用于转换范围为0至255之间。显然,从程序员的观点,对温度进行直接的处理要比使用由ADC所产生的与一给定温度相一致的值要容易。接口总是用于读在微机和接口元件之间进行传送。根据这些理由,通常使用子程序来监督接口的具体操作,并完成任何所需的量程调整和/或线性化。

数字接口电路

在微机电路中使用的信号几乎总是太小而不能被直接地连到“外部世界”,因而必须用某种形式将其转换成更适宜的形式。接口电路部分的设计是使用微机的工程师所面临最重要的任务之一。我们已经了解到微机中,信号以离散的位形式表示。当微机要与只有打开或关闭操作的设备相连时,这种数字形式是最有用的,这里每一位都可表示一开关或执行器的状态。

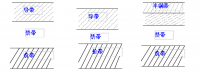

连接逻辑电路时,必须小心翼翼,以保证它们的逻辑电平和电流额定值是兼容的。由逻辑电路产生的输出电压通以拉出或灌入最大额定电流时,按最弱情况下数值所定义。这样VOH是当拉出最大额定“高”输出电流IOH时的允许最小“高”电压,而VOL则是当灌入最大额定“低”输出电流IOL时允许最“低”电压。对逻辑输入也有相应的参数,规定最小输入电压为逻辑“高”状态VIH,以及最大输入电压为逻辑“低”状态VIL。

对于输入接口,也许设计所面临的主要问题是电噪声,小噪声信号会引起系统工作不良,而大量的噪声会造成永久性损坏。设计者必须从一开始就清楚这些危险。有许多方法保护接口电路和微机不受各种各样噪声影响,下面是一些例子:

1 使用光电隔离或变压器实现微机系统和外部器件之间的输入输出电信号隔离。

2 用一低通滤波器和施密特触发器排除高频噪声脉冲。

3 用一对二极管以反向偏置于正常方向的形式连接至电源端,来保护过高的输入电压。

对于输出接口,一逻辑器件的参数VOH,VOL,IOH和IOL往往太小而不能直接与负载相连,实践中必须在一个外部电路将电流和电压进行放大以驱动一负载。现在尽管有一些类型的半导器件可用于将DC和AC的功率控制至若干千瓦,有两种基本方式将开关连至负载,并对其进行控制。

对于串联连接,开关闭合时使电流流过负载,而当并联连接时合上开关使电流绕过负载。两种方式都可用于低功率电路中,但只有串联连接才能用于高功率电路,这是因为串联电阻R上要消耗功率。

反馈控制

这里所研究的这一类控制问题,在工程上具有相当重要的意义。我们所讨论的系统有几个输入,其中某些输入称为控制量,因为这些量是可以人为地控制的,而另一些输入称为外部扰动,它们是很难预知的。例如在工业用加热炉中,可以认为燃料流量、环境温度以及炉内材料装填量都是输入量,其中燃料流量是容易测量和容易控制的,但后面两项通常是不能预知的扰动。

芯片多处理技术

芯片多处理是CPU设计中即将商品化的技术,它把两个或更多的处理器内核做在一个硅片(称做衬底)上,以增强计算性能,使之超过有单个或多个分立CPU的服务器。它也称做“芯片上多处理”或“芯片上多处理器系统”。

明年早些时候,顶级的强力用户将发现“三个臭皮匠顶个诸葛亮”。到那时,Sun、IBM、Compaq、HP和其它的公司将开始推出利用芯片多处理(CMP)技术的高档服务器,这是从目前的将多个分立芯片模块装进机箱的系统向前迈进了一步。(引人注目的是这个集团中没有英特尔公司,它将赌注下在增强速度的指令级并行处理上,它是一种成本较低的提升性能技术。)

加州山景市的微处理器咨询公司The Linley Group的首席分析师Linley Gwennap称,“其驱动力不是设计更复杂的处理器,为什么不把两个放进同一模块?”他还说,随着时间的推移,操作系统能支持多处理芯片,但编程的障碍很难克服。

早期的测试表明,单个模块中的两个处理器比多个分立处理器的性能提高50%以上。把两个CPU放到单片硅片上,当在两个CPU之间传送数据时,就能利用更短的距离和更快的总线速度。据位于德州奥斯汀市的IBM服务器集团的技术总监Joe Tendler称,IBM的产品(叫Power4处理器)达到每秒处理100GB的数据能力,这相当于每秒处理20张满容量的DVD。

类似这样的数据处理就可能带来天价的系统—几十万乃至几百万美元,这将直接把CMP系统送到高档的技术和商业市场,包括为石油勘探公司处理地震数据的机器、能处理没法预测的流量负荷和高峰的电子商务服务器、数据密集的图形处理器硬件以及处理基因数据的计算机。

然而不是每一种高端应用都适合用CMP的。财务上顺序地处理一个分类账人物的批处理程序仍只能依靠单处理器相同。

由于芯片制造技术不断改进、允许更高密度地封装集成电路,商业上可行的CMP系统的时代已经到来。(省出的)额外衬底面积为多个CPU腾出了空间—最初的系统中有两个CPU、但在以后的几代CMP模块中可多达8个CPU。

但只简单地把两个橡皮塞进一个封装块并不一定能做出高效得多处理器。对工程师来说,最大的挑战实施有两个头的发电厂(即处理器)烧掉数据(即处理数据),这就是将在芯片厂家之间浮现出来的最大的设计差别。

预定下一个季度问世的Sun公司的MSJC-5200模块将包括两个500MHz的CPU和一个数据传输引擎。峰值I/O的数据传输率为4.8GB/ps。处理器共享16KB德路成组相连的数据高速缓存,每个CPU还有自己的16KB 2路成组相连的指令高速缓存。

MSJC-5200中的另一项诀窍是多线程:硬件能将处理任务分成以字节为长度单位的数据块,它们以有序的方式输送到每个(处理器)内核,以避免丢失任何处理周期。但是很多软件应用不能优化为多线程。为补偿之,MAJC-5200利用Java虚拟机有选择地在Java程序中生成线程。

于此相反,IBM在其速度更高的1GHz的Power4芯片中没有采用多线程。为使数据有效传送,把每个CPU中32MB的存储器分为二级和三级的高速缓存,以保持CPU到CPU的通信流畅,并缓冲从系统内存中检索到的信息。

虽然最初的Power4系统是为大于1GHz的总线速度设计的,以便适应随时间的推移处理器越来越高的速度,但该系统将使用500MHz的总线速度,即只有处理器钟频的一半。

Sun和IBM两家公司一致的地方是:芯片多处理是CPU设计的下一个大动作。过去,工程师们利用更好的工艺技术、更好的微体系结构和更好的编译器设计更快的性能。芯片多处理增加了另一个提高性能的工具,直接针对处理器发展的要害。

芯片多处理器技术有可能将工业界带进超越摩尔定律的时代。这对大用户来说是好消息,但对软件程序员来说却是更多的挑战。