英特尔STRATAFLASH™内存技术的发展与应用

1.0引言

因特尔的创新和技术领先地位是建立一个新的先进的非易失性内存技术的基础——英特尔StrataFlash™内存。 英特尔StrataFlash™内存技术通过在每个闪存单元存储多个比特来显著地增加了单位面积的比特数。这有效地降低了闪存整体每兆字节的成本。英特尔StrataFlash™技术建立在英特尔前四代ETOX™闪存工艺上,学习和利用了数十年积累的叠栅存储器单元的制造经验。

英特尔的NOR-based,Multi-level单元技术提供了直接的存储单元访问,这是必不可少的提供准确的电荷检测,排列和存储。这是英特尔StrataFlash™内存技术的三个关键方面。这种直接存储单元的访问是可靠的,强大的技术,适用于许多的应用。

英特尔StrataFlash™内存技术使用尖端科技和算法来编写,读和擦除。这些闪存结合了EPROM型编程和类似系统内电擦除。把存储器划分为更小的门阵列块,配合片编程和擦除算法的自动化,加上已经高效和可靠的闪存的优点使已经高效和可靠地闪存更具优势。这项功能结合了英特尔积累多年的制造经验,电气试验和温度应力数据的收集,先进的设计架构技术,创新带来了高可制造,可靠和划算的闪存。

英特尔考虑到产品的技术开发和使用的许多方面,平衡元件尺寸的大小,阵列结构和系统设计,进而产生一个强大和多功能的多层存储单元。这个文件描述了英特尔StrataFlash™内存技术的基本情况,提供存储器写、读、擦除的工作特性。除此之外,它还简要的描述了使用英特尔StrataFlash技术的系统的执行优点。

1.1标准ETOX™闪存技术

典型的闪存都使用单比特每单元。每个单元使用一个特定的阈值电压或者电压等级。电荷储存在每个单元的浮栅中。在每个单元或晶体管中,存在两个可能的电压水平(图1,a)。这两个电压水平被写程序产生的电荷或储存在浮栅上的电荷所控制;如果浮栅上电荷的数量达到一个参考的电压水平,这个单元就被认为进入了另一个电压水平。

1.2英特尔StrataFlash™存储技术

英特尔StrataFlash™存储器是一个使用了Multi-Level单元(MLC)。通过改变晶体管多晶硅浮栅的电压水平,MLC能够实现每单元多比特存储。英特尔的MLC技术通过指定一个特别电压范围内的位形式,采用了传统闪存的自然模拟的优点。这个技术有效的减少了储存单元面积和对于一个给定密度的芯片大小。这最终导致了每兆字节单位成本显著地减少——这是这个技术的最大好处之一。英特尔StrataFlash™存储器产品能每单元存储两比特(图1,b)。英特尔StrataFlash™技术路径举例说明了NOR-based MLC 技术很容易扩展至每单元三比特(图1,c),从而使显著地增加单位面积的密度。

在英特尔StrataFlash™技术中,通过每个单元的电压被分为大于两个电压水平的电压。图1举例说明了每单元两比特和三比特技术的Vt电压水平分配。

1.3存储单元结构

用于ETOM闪存和EPROM技术中的一个多晶硅浮栅(poly1)提供电荷储存。英特尔的超纯薄氧化层形成技术产生一个低缺陷的隧道氧化层,把浮栅和硅表面分离出来的。

存储单元结构包含一个直接在浮栅上的poly2控制栅。一个ONO介质分隔开了浮栅和控制栅。浮栅在它自己和源区或漏区之间有另外的一个绝缘层。一个介质层分隔开金属1和控制栅。这个控制栅硅化物,能减少字线电阻。

一个缓变的源扩散提高擦除效率。这个缓变源扩散通过磷注入进入源区。深注入在擦除期间,通过阻止源区或氧化层击穿也能提高可靠性。

金属1携带着位线信息到检测放大器,同时,路线电压也到达存储单元的源极。金属2携带着字线信息减少它的电阻。这项技术增强了存储器的读取(tACC)性能和信号的工艺路线,以及写操作电压和擦除电压。双金属技术提高了访问次数,因为它使阵列更紧促。通过使用更紧促紧凑的晶体管版图和EPI晶圆工艺,读取访问计时时间也被改良。新材料提高了掩膜层通过狭窄的接触孔的互连。

2.0存储单元的工作原理

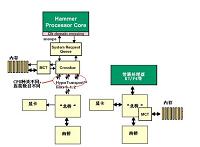

英特尔StrataFlash™存储器必须能精确的控制电荷。更特别地讲,英特尔StrataFlash™存储器必须能精确的放置电荷,精确的检测电荷和及时的存储电荷。通过NOR结构的直接连接每个存储单元的栅极,源极和漏极,这些要求能被满足。每个存储单元由单个晶体管构成,晶体管直接与要完成精确操作的控制电压相连。

2.1写操作

在写操作过程中,浮栅上必须要有准确的电荷。模拟电压加在每个闪存单元的被浮栅上的电子控制的不同电压水平上。沟道热电子(CHE)的注入控制着这些电荷的放置。

在写操作过程中,每个存储单元的直接地、位线和字线的连接能精确的控制电荷的放置。每个存储单元的控制栅连接内部的电源电压,这个电源电压通过直接的字线连接和行译码来产生。漏极连接一个恒定的电压,这个电压通过直接的位线连接和列译码来产生。而源极直接接地。

加在控制栅上的电压通过电容耦合到浮栅上。这个耦合到浮栅上的电压就是偏置电压,相应的它使在浮栅下的P型沟道反转。在沟道反转(现在是N型材料的特性)后,一个中间的电压水平加在漏极上。这导致漏区从源区吸引N型材料中的主要载流子电子,

写操作通过加速沟道中的电子获得足够的能量去克服隧道氧化物的势垒而完成。随着漏电压的增加,沟道电子获得更高的漂移速度,从而增加了电子的动能。这些沟道中的电子会和衬底原子碰撞,激活硅晶格。当沟道电子不能足够快的转移它们的动能给硅原子时,便保持热平衡。因为能量是守恒的,电子开始变“热”,并朝多个方向运动。通常,电子聚集足够的能量时,便能克服3.1eV(电子伏特)的隧道氧化物势垒,积累在浮栅上。使用一个精确的偏置栅电压能确保热电子会被注入浮栅。

电子存储在浮栅上产生了一个能被控制栅克服的静电势。这个静电势导致了一个对晶体管(存储单元)而言的高的开启阈值电压。坦白地说,精确的栅极和漏极控制对英特尔StrataFlash™存储单元的放置时很关键的。

在英特尔StrataFlash™存储技术中,通过每个存储单元的电压被分为多个电压水平。图4举例说明了存储单元分配的各个分立的电压水平,和对于每单元两比特技术设置的参考点(P1,P2,P3)。在写操作过程中,一个特别地电压范围被用来代表一个特别地电压水平。对一个给定的存储单元写数据,从“11”(擦除)水平到“10”、“01”或“00”(写数据)水平。每单元存储两比特要求定义四个参考水平,参考点为R1,R2,R3。这些电压水平被定义为读取参考单元的阈值电压。如下,Vt<Vt(R1)为水平0,Vt(R1)<Vt<Vt(R2) 为水平1,Vt(R2) <Vt <Vt(R3) 为水平2,Vt(R3)<Vt为水平3。特别地,惟一的电压值对应相应的电压水平。

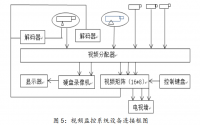

英特尔StrataFlash™存储写算法被应用在单片的写状态机(WSM)上。获得专利的写算法发展为对栅电压和漏电压的精确控制,从而提供非常准确和可重复生产存储单元的阈值电压控制。当写操作完成时,WSM更新STS的内部状态寄存器,并指示STS确认。另外的状态字详细的讨论了写成功或错误的信息,若错误,还会指出可能失败的原因。图5举例说明了写程序的各个时期。

2.2读操作

在读取数据的时,电荷检测是最重要的。通过直接连接各个存储单元,数据读取操作能快速、准确和可靠的确定各个存储单元的电压水平。读取速度同每单元一比特技术相当。

数据读取操作检测基于三个参考单元的阈值电压的四个不同的电压水平。这些参考单元偏置在这样的一种方式——每个偏置产生与它的特定电压水平Vt 成比例的电流。在读取操作时,VREAD接控制栅极,源极接地,漏极接偏置电压。在这种模式下,每个单元的电流Icell与电压Vt成比例。

当每个存储单元偏置在这种情况下时,通过每个存储单元的电流与它的电压Vt反向。因此,如果通过存储阵列的电流就大于参考电流(Icell >IR#Ref ),此时,存储单元的电压Vt 就小于参考单元的电压Vt (VtCell <VtRef )。通过存储单元的电流和参考单元的电流的比较,数据就被读了出来。

存储单元的位线电流和参考电路产生的参考电流进行比较,电流会被连接漏极的有源负载检测到,有源负载连接不同的检测放大器。对于数据读取操作,有一个检测放大器连接每个参考单元。每个检测放大器有一个来自位线的闪存阵列输入和参考单元的输入。如果ICell > IR#,检测放大器就输出逻辑“1”。

三个检测放大器的输出连接能同时翻译两个位数据的逻辑电路。如果存储单元是电压水平1,也就是ICell >IR1Ref ,这时,所有的检测放大器均输出逻辑“1”,同时,逻辑电路输出数据“11”。在电压水平1,IR2Ref < ICell < IR1Ref ,因此检测放大器2和检测放大器3就输出逻辑“1”,检测放大器1就输出逻辑“0”,逻辑电路就输出数据“10”。在电压水平2,IR3Ref < ICell < IR2Ref ,因此检测放大器1和检测放大器2就输出逻辑“0”,检测放大器3就输出逻辑“1”,逻辑电路就输出数据“01”。在电压水平3,ICell < IR2Ref ,所有的检测放大器全都输出逻辑“0”,逻辑电路就输出数据“00”。

检测操作描述了数据的读取操作。同样,这也适用于写数据和擦除操作。在写操作时,检测操作只是确保存储单元能达到相应的电压水平。同样的,在擦除操作时,检测操作只是确保存储块被完整的擦除掉。

2.3擦除

擦除操作通过用Fowler-Nordheim隧道击穿工艺,在隧道氧化物上加一个高电场来完成。被擦除掉的存储单元全都变为了电压水平0(数据“11”)。在擦除操作时,正电压连接需要擦除的存储单元块的所有源极,控制栅极连接负电压,漏极连接

当一个存储单元偏置在这种形式下时,电子就预先存储在了浮栅上,并吸引源极。电子穿过薄的氧化层,相应的减少存储单元上Vt ,通过类似写操作的方法,这个Vt被证实小于Vt(EV) 。

首先,块中的所有存储单元起初是预先的或写过的。在预先的完成后,WSM就开始用一个脉冲进行实际的擦除操作。在每个闪存单元的源极加一个脉冲,就完成了擦除。在发出每个脉冲后,WSM就会对擦除块中所有字地址的数据与数值FFH进行比较。数据地址的选择是靠内部地址计数器完成的。

当一个字节的位置没被核实时,WSM就会停止内部的边缘检测或数据比较功能,就会有另一个脉冲对其进行擦除。对所有位置检查完后,就会进行重新检测。如果检查没问题,就开始地址测序和验证测试;如果有问题,另加脉冲擦除。在这项测试中,重复加脉冲擦除和重复测试会一直继续,直到所有要擦除的存储单元被确认擦除。和写操作一样,在擦除完成后,WSM会更新状态寄存器的STS和硬件的STS。

这里需要注意的是,NOR型闪存器不包含EEPROM技术的两个晶体管一个存储单元,它们不能字节粒度的擦除。反而,闪存擦除是以块(MLC是128KB)进行的。这意味着许多存储单元浮栅上的电荷是同时耗尽的。

微信

QQ1:3097331788 QQ2:2601997959 QQ3:2993773635