基于FPGA的数字锁相环的设计与仿真

【摘要】本设计是设计一种二阶数字锁相环,使用比例—积分算法代替传统锁相环路系统中的环路滤波,并使用相位累加器实现数控振荡器的功能。在实际工程中所应用的锁相环无论其功能和结构有何差别,其基本结构应该都由三个基本部件(鉴相器、环路滤波器和压/数控振荡器)构成。本设计的主要任务就是沿用此基本结构,在具体实现上采用了全新的控制和实现方法来设计这三大模块。该锁相环由FPGA实现,采用Quartua II和Modelsim SE作为软件开发环境,其灵活性、速度优化和资源控制都能够更好的体现。设计调试好此系统后,需进行后期的锁相环数据分析,记录分析的数据主要包括:分析锁相环系统的稳定性;分析系统的跟踪误差;通过调节比例和积分系数以调节系统稳定性和锁相速度,做好分析图表。

【关键词】数字锁相环(ADPLL),比例积分,FPGA ,环路滤波

第一章 绪论

1.1 简述锁相环路

锁相环路(PLL)是一个能够跟踪输入信号相位的闭环自动控制系统,它在无线电技术的各个领域得到了很广泛的应用。锁相环路有其独特的优良性能,它具有载波跟踪特性,作为一个窄带跟踪滤波器,可提取淹没在噪声之中的信号;用高稳定的参考振荡器锁定,可作提供一系列频率高稳定的频率源;可进行高精度的相位与频率测量等等。它具有调制跟踪特性,可制成高性能的调制器和解调器。它具有低门限特性,可大大改善模拟信号和数字信号的解调质量。70年代以来,随着集成电路技术的发展,逐渐出现了集成的环路部件、通用单片集成锁相环路以及多种专用集成锁相环路,锁相环路逐渐变成了一个成本低、使用简便的多功能组件,这就为锁相技术在更广泛的领域应用提供了条件。

锁相环是一个相位误差控制系统。它比较输入信号和振荡器输出信号之间的相位差,从而产生误差控制信号来调整振荡器的频率,以达到与输入信号同频同相。所谓全数字锁相环路(DPLL)就是环路部件全部数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)构成的锁相环路,

本课题是设计一个由单片机、定时计数器及单片机集成锁相环路组成的可程控频率合成器,所以设计过程会涉及到锁相环路、频率合成器和单片机方面的知识。

1.2 锁相技术发展概况

锁相原理在数学理论方面,早在30年代无线电技术发展的初期就己出现。1930年己建立了同步控制理论的基础。1932年贝尔赛什(Bellescize)第一次公开发表了锁相环路的数学描述,用锁相环路提取相干载波来完成同步检波。到了40年代,电视接收机的同步扫描电路中开始广泛地应用锁相技术,使电视图像的同步性能得到很大改善。进入50年代,随着空间技术的发展,由杰斐(Jaffe)和里希廷(Rechtin)利用锁相环路作为导弹信标的跟踪滤波器获得成功,并首次发表了包含噪声效应的锁相环路线性理论分析的文章,同时解决了锁相环路最佳化设计问题。在60年代,维特比(Viterbi)研究了无噪声锁相环路的非线性理论问题,并发表了“相干通信原理”一书。到70年代林特塞(Lindscy)和查利斯(Charles)进行了有噪声的一阶、二阶及高阶锁相环路的非线性理论分析,并作了大量实验以充实理论分析。

锁相环路具有许多优良特性,它可用于频率合成与交换、自动频率调谐、模拟和数字信号的相干解调、AM波信号的同步检波、数字通信中的位同步提取、锁相稳频、锁相倍频与分频、锁相测速与测距、锁相FM (PM)调制与解调、微波锁相频率源及微波锁相功率放大器等。目前,锁相环路的理论研究正日臻完善,应用范围遍及整个电子技术领域。现在锁相环路正向着集成化、数字化、多用途、系列化、高速度、高性能方向迅速发展,且商品化集成锁相环路日益增多,为锁相技术应用提供了广阔前景。

目录

第一章 绪论 5

1.1 课题背景及意义 5

1.2 国内外相关研究状况 6

1.3 FPGA技术与Verilog HDL语言简介 7

第二章 软件方案选择论证 8

2.1 鉴相器(DPD)程序设计实现方案 8

2.2 环路滤波器(DLF)的程序设计的实现方案 9

2.3 数字振荡器(DCO)的程序设计的实现方案 9

2.4 FPGA程序设计实现方案 10

2.5 软件设计系统时钟的选择 10

第三章 锁相环系统介绍 10

3.1 锁相环系统的分类及性质 10

3.1.1 模拟锁相环 10

3.1.2 数字锁相环 11

3.2 锁相环的性质 11

3.2.1 带宽 11

3.2.2 线性 12

3.3 锁相环的工作原理与结构 12

3.3.1 鉴相器(PD) 12

3.3.2 环路滤波器(LF) 13

3.3.3 压控振荡器(DCO) 14

3.3.4 环路相位模型 15

3.3.5 环路的动态方程 15

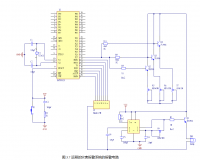

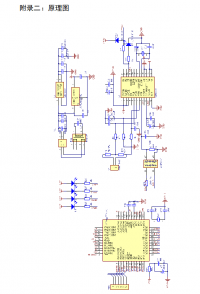

第四章 锁相环系统的软件设计及仿真 17

4.1 系统软件设计要求 17

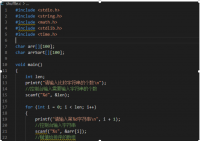

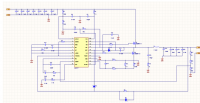

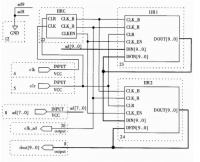

4.2 数字鉴相器(DPD)的软件设计及仿真 17

4.3 数字环路滤波器(DLF)的软件设计与仿真 19

4.4 数控振荡器(DCO)的软件设计与仿真 21

4.5 锁相环系统软件设计中遇到的问题及解决方法 24

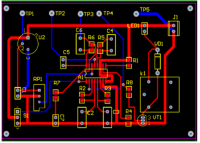

第五章 锁相环系统的硬件环境及调试 25

5.1 锁相环系统的硬件环境:Altera DE2开发板的介绍 25

5.2 锁相环系统的载入DE2开发析调试 25

5.3 锁相环系统硬件调试所遇到的问题及解决方法 25

第六章 锁相环系统相关参数的分析确定及数据的测试分析 27

6.1 锁相环系统相关参数的分析确定 27

6.1.1 锁相环系统比例参数PG、积分参数IG的确定 27

6.1.2 锁相环系统比例和积分计数限幅参数、控制参数N限幅参数的确定 27

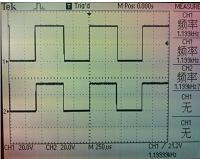

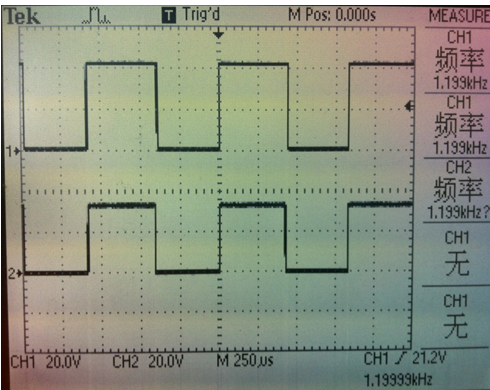

6.3 数字锁相环系统数据的测试分析 28

6.3.1 锁相环系统的稳定性分析 28

6.3.2 锁相环系统跟踪误差的分析 32

6.3.3 调节比例积分系数来分析系统的稳定性和锁相速度 34

总结 38

致谢 39

参考文献 40

参考文献

[1]胡华春,石玉.数字锁相环路原理与应用[M/CD].上海科学技术出版社.1990.

[2]潘松,黄继业.EDA技术与VHDL[M/CD].清华大学出版社.2009.

[3]赵杨.基于FPGA的数字锁相环设计研究[J].光电技术应用,2006年第6期.

[4]庞浩,王赞基,陈建业. 一种数字锁相方法[P]. 中国发明专利. ZL01131095.2 ,2001-9-21,2003年授权.

[5]魏选平.锁相环工作原理及仿真分析[J].电子测试,2011年第6期.

[6]张厥盛,郑继禹,万心平.锁相技术[M/CD].西安电子科技大学出版社.1994.

[7]庞浩,王赞基.一种状态转移时序逻辑的信号鉴相方法[P].中国发明专利ZL01142025.1,2001-9-7,2003年授权.

[8]庞浩,王赞基.一种基于FPGA实现的数字锁相环[J].电子技术应用,2005年第5期.

http://www.bysj1.com/

http://www.bysj1.com/html/4408.html http://www.bysj1.com/html/4416.html http://www.bysj1.com/html/4406.html http://www.bysj1.com/html/4398.html