NiSi薄膜工艺控制研究分析(材料专业论文)

高掺杂衬底硅化问题

由于大量的杂质存在于高掺杂硅衬底中,所以其Ni 硅化物形成工艺需要考虑杂质对硅化物形成过程的影响,硅化物形成引起杂质的重新分布,杂质和硅化物的混合物形成,杂质分凝现象和Si 缺陷问题等。其中,最主要的是杂质的再分布特性。

在硅化物形成过程中,杂质倾向于离析在低能量的位置,如表面、界面、晶粒边界和空位处等。以Ni/Si 结构的两步硅化工艺为例,在Ni2Si 向NiSi的相变过中,由于存在体积变化而在Ni2Si/NiSi界面处形成大量空位,导致杂质离析,形成高浓度杂质分布区。此外,由于杂质在硅化物和Si 中的固溶度差异而产生的杂质分凝现象,将在NiSi/Si 界面处形成高浓度杂质分布区,而且其杂质浓度随退火温度的降低而减少,所以低热预算有利于减少杂质在退火过程中的损耗【5】。

5.3.2 SOI 衬底硅化工艺

SOI 技术作为一种全介质隔离技术,具有许多体硅技术不可比拟的优越性,如高速、低功耗、抗干扰能力强和适合小尺寸器件等优点,因此已成为亚100 nm CMOS 技术的主流工艺技术之一。与SOI衬底相关的镍自对准硅化物形成工艺同样得到广泛的研究。

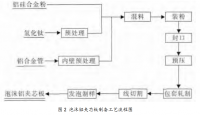

在SOI 技术中,器件仅制造于表层很薄的硅膜中,所以自对准硅化物工艺需要精确控制初始Ni 膜厚度和RTA1 工艺条件。如果RTA1 后形成的富镍相硅化物过少,将导致RTA2 后NiSi 膜厚度变薄,导致大的源漏电阻;如果RTA1 后形成的富镍相硅化物过多,将导致RTA2 后NiSi 膜向沟道延伸,形成过度硅化,导致源漏侵蚀(如图9 所示) ,使泄漏电流增大。此外,由于SiO2 和Si 的热膨胀系数不同,所以,表面硅膜越薄,则引入的张应力越大,有利于原子在表面的扩散,促进硅化物的形成,引起过度硅化问题

图11 源漏过度硅化图示

对于SOI 衬底,可以通过降低RTA1 的退火温度和采用Pt 掺杂的Ni 硅化物,改善NiSi 形成时在源漏方向的侵蚀作用,同时提高NiSi2 相形成温度。

5.3.3 NiSi 热稳定性问题

研究人员已经使用Pd、Pt 、Ti 、Zr 、Ta 、Mo 、Hf 、Ru 、V、Co 和Se 等金属,采用Ni/X/Si 或X/Ni/Si的叠层金属结构来改善NiSi 膜的热稳定性,其中,X 为其他金属,但是并没有得到理想的结果。

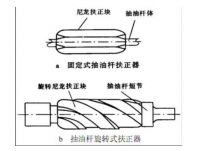

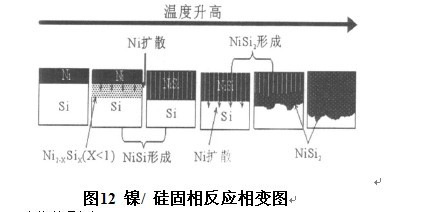

K. Nagahiro1 等人提出硅化物形成后金属掺杂工艺( PSMD 工艺) 改善NiSi 膜的热稳定性,其热稳定性增强原理如图12 所示, Pt 和Hf 的加入有利于提高热稳定性。

图12 镍/ 硅固相反应相变图

5.3.4 应力对NiSi 硅化的影响

研究表明,衬底中的压应力抑制Si 原子的扩散,抑制硅化物形成;而衬底中的张应力促进Si 原子的扩散,有利于硅化物形成。所以,压应力的硅衬底抑制NiSi 和NiSi2 的形成,而张应力的硅衬底促进它们的形成。通过工艺控制衬底应力,有利于优化NiSi 形成工艺。

5.4 自对准金属硅化物制备的可能问题点

5.4.1 栅电极与源/漏极扩散区桥接(Bridging) 问题

Ti与SiO2 在700℃以上反应生成不易为NH4OH及H2O2溶液去除之化合物(如C49-TiSi2,C54-TiSi2),因此700℃为形成SALICIDE 时RTA1 之温度上限。一般为尽可能得到最低之电阻值,都想尽办法提高这个温度上限。另由于硅元素为硅与钛界面反应时之主要扩散元素,如果RTA1 之温度、时间、气氛控制不理想时,容易造成栅电极多晶硅到源/漏极间介电质侧壁层上形成C49-TiSi2 及C54-TiSi2等化合物,即所谓的桥接现象,导致元件失效。由于这种桥接源于硅原子沿钛与氧化硅界面上之横向扩散及反应结果,RTA1 之温度与时间需互相配合, 即越高温配越短时间,越低温可越长时间,大抵可从650℃,120s 到700℃,20s,含氮之反应气氛也扮演一重要角色,因为氮之加入于Ti晶粒边界上可有效抑制硅之沿晶界扩散而减缓桥接发生的可能,同时氮与钛易于表面生成一有效防止氧气进入参与反应又容易以选择性化学溶液去除之TiN薄层。

在前面的TiSi2工艺步骤中,就已经就这一问题提出避免出现的方案,减少RTP1的时间,在N2气中进行。当然这个问题只要控制的好,这个问题是很容易避免的。

5.4.2 扩散区结漏电流(Junction Leakage) 问题

VLSI 元件尺寸越来越小,源/漏极区与井区(Well) 之间的结深越来越浅,如0.5 微米元件之结面深度已小于0.2 微米;另一方面,为求较低之电阻值,希望SALICIDE 越厚越好。经验发现,SALICIDE 厚度不能大于结深深度之一半,否则结漏电流相当严重。 一般为解决短通道效应(Short Channel Effect) 所增加之反突穿植入更增加SALICIDE 厚度之限制。在金属钛溅镀时,同时镀上一层薄TiN层可较容易控制SALICIDE 厚度及均匀度,间接的可以减少结漏电流。另外后续热处理温度的控制也极为重要,太高之后温如900℃,30min 以上可能使SALICIDE 发生团缩而突穿界面。

这种植入,还可在源/漏极区当作降低硅/钛反应能障之用。一般已因TiSi2为低电阻值化合物,栅电极多晶硅及源/漏极区之掺杂浓度概可降低至一半以下,若配合薄TiN层之加镀,这种因掺杂浓度及型态不同对SALICIDE 形成厚度之影响可降至最低。

5.4.3 SALICIDE 之高温稳定性的问题

许多实验结果显示,后温温度太高或时间太长皆易造成SALICIDE 团缩现象,不但可能影响接面漏电流,造成连接线之高电阻值问题,甚至下一层导线到SALICIDE 之接触电阻值都会因而升高。研究发现,越厚、越宽之SALICIDE,其高温稳定性越佳。然而在VLSI 时代,元件的需求是越薄越细,因而SALICIDE 制程之后温受到严格限制,如金属制程前介电质层之密化温度需尽可能降低或以RTA 取代之,最好是完全取消超过700℃之后温。

5.4.4 狭小区域上之相转换(Phase Transformation) 问题

次半微米VLSI 时代,继续以TiSi2 为SALICIDE 材料之困难点主要在低电阻值相C54-TiSi2 之形成温度,即C49-TiSi2转变成C54-TiSi2 之温度,随SALICIDE 之厚度及线宽越小而越高。另一方面,越高温反应越容易使又薄又窄的SALICIDE 形成团缩现象,这种两难的问题一直挑战技术开发者。迄今有多种改进方法如

1. 金属钛溅镀前之表面非晶化(Amorphization) 用以增加硅/钛反应成核点(Nucleation Site) 或减小C49-TiSi2之晶粒大小;

2. 在金属钛溅镀时维持晶片表面于300℃ 以上之高温以利硅/钛之先期交互扩散(Interdiffusion) 及使用高纯度之钛金属靶;

3. 利用选择硅沉积(Selective Silicon Deposition) 于栅电极与源/漏极区再做表面非晶化处理,一举解决结漏电流,掺杂浓度及型态不同对SALICIDE 形成厚度之影响及相转换困难等问题。

4. 在栅电极使用耐高温又无相转换问题的WSix POLYCIDE,而只在源/漏极区形成SALICIDE;

5. 寻找其它没有相转换问题的SALICIDE,如CoSi2 或NiSi。不过这两种SALICIDE 除了高温稳定性较Ti SALICIDE 差之外,Co 主要之缺点在对硅晶表面自生或残留氧化硅相当敏感,本身为磁性材料而在一般溅镀机台沉积速率极慢等。

微信

QQ1:3097331788 QQ2:2601997959 QQ3:2993773635