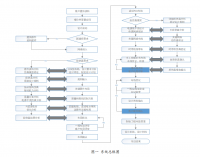

32位微机实验系统的结构分析与研究

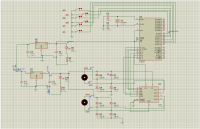

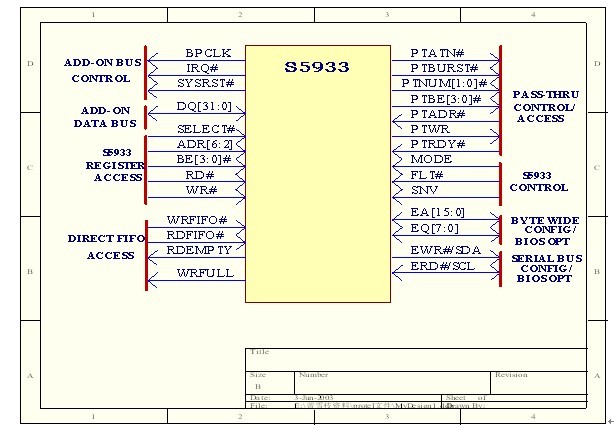

系统为32位微机原理和微机接口技术应用分别提供了实验于台。32位微机原理部分实验平台由一组支持在80386、奔腾及其以上PC 微机上的编程及调试工具组成。微机接口应用部分,系统提供了硬件实验平台,并将实验分为基本接口和高级接口应用两部分。对于基本接口应用学习,系统经PCI总线扩展卡及转接逻辑为用户提供了一个仿真ISA接口,用户可以基于该接口学习常用接口芯片的编程及应用; 对高级按口部分的学习,实验系统提供了全开放的简化PCI总线接口-ADD-ON总线接口及CPLD实验单元,使用户可以直接对PCI总线完成特定应用需要的接口设计,和PCI总线应用扩展实例。32微机实验系统使用了三种总线:PCI BUS(见附录1),ADD-ON BUS(见附录3)以及ISA BUS的部分信号。通过AMCC S5933实现PCI到ADD-ON的转换并通过逻辑组合提供ISA的部分信号。

2.1 32微机实验系统的功能

1. 完善的基本微机接口技术实验教学平台

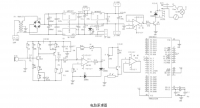

系统以PC 微机为主机,通过PCI总线扩展卡将PCI总线信号经扩展卡上的PCI总线控制芯片进行转换,转换成ADD-ON总线信号引入接口实验平台,再经过逻辑转换而形成仿真ISA总线接口,供作基本接口实验使用。在接口实验单元中,系统提供了各种常用外围接口及其控制应用部件,如定时/计数器8254、并口 8255、串口 16550、静态存贮器 6264、闪存 29256、AD574、DA0832、键盘输入及 LED显示、二进制开关输入及发光管显示、电机及温度控制单元电路。

2. 可支持PCI总线扩展开发的高级接口技术实验平台

系统以PC 微机为主机,通过PCI总线扩展卡将PCI总线信号经扩展卡上的PCI总线控制芯片进行转换,转换成ADD-ON总线信号引入接口实验平台,并提供CPLD应用开发单元,使用户可以进行各种硬件接口逻辑的设计,由此进行PCI总线扩展应用实验及PCI总线的扩展应用开发。

3. 系统提供了FLASH闪存,体现先进存贮技术。

2.2 32微机实验系统的单元结构

2.2.1 实验箱单元结构及其功能

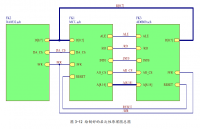

1. ADD-ON总线单元(ADD-ON BUS UNIT)

提供所有的ADD-ON总线信号。以供进行高级接口实验所需。

2. 仿真ISA接口单元(SIMULATION ISA INTERFACE)

该单元提供的仿真ISA接口信号,用于进行低级接口实验。

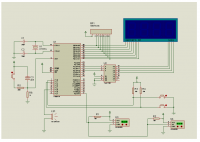

3. 8254定时/计数器实验单元(8254 UNIT)

主要芯片:8254定时/计数芯片

主要实验:1.. 计数应用实验 2..定时应用实验 3..电子发声装置

4. 8255并行接口实验单元(8255 UNIT)

主要芯片:8255并行口芯片

主要实验:1.. 基本输入输出实验 2..流水灯显示实验 3..键盘及显示实验

5. 16550串行接口实验单元(16550 UNIT)

主要芯片: 一片16550串口芯片,并配有标准RS232C串行通信接口

主要实验: 1..串行通信基础实验 2..串口自发自收应用实验 3..与PC串口通信应用实验 4..串口双机通信应用实验

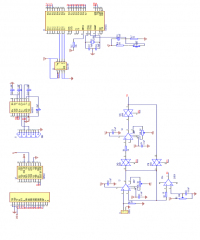

6. 574 A/D转换实验单元(ADC UNIT)

主要芯片: ADC574芯片及其电位器电路

主要实验: A/D转换实验

7. 0832 D/A转换实验单元(DAC UNIT)

主要芯片: DAC0836芯片和LM324芯片

主要实验: D/A转换实验

8. 键盘及LED显示实验单元电路(LED-KEYBOARD UNIT)

主要构成: 由4个共阴数码块、2行4列键盘和LED 驱动器电路构成

主要实验: PCI中断应用实验

9. 静态存储单元(SRAM UNIT)

主要芯片: SRAM6264芯片

主要实验: 静态存储器扩展实验

10. FLASH ROM存储单元(FLASH ROM UNIT)

主要芯片: FLASH ROM 29C256

主要实验: FLASH ROM 扩展实验

11. 电子发声实验单元(SPEAK UNIT)

主要构成: 由一只蜂鸣器和驱动电路构成

12. 电机控制实验单元(MOTOR UNIT)

主要构成: 由ULN2803电机接口芯片、一台四相八拍步进电机、一台DC12V直流电机及霍尔测速电路构成。

主要实验: 1.. 步进电机实验 2..计算机综合控制应用实验

13. 微型温度控制单元

主要构成:由7810芯片产生+10V的稳定电压和一个51欧的电阻构成

回路。

14. CPLD单元(PLD UNIT)

主要芯片: LATTICE ispLSI1032

主要实验: 1.. 访问S5933操作寄存器实验 2..邮箱应用实验 3..访问PASS-THRU区域实验 4..用FIFO实现总线DMA实验

15. CPLD下载单元(PC DRIVER)

主要构成: 此单元位于实验极左部,芯片编程时,用专用电缆将PC机并口连至PC-PORT排针,而将E-PLD排针连至 PLD UNIT单元的 EPLD单元相应排针即可。

16. 开关及发光二极管显示灯单元(SW-LED UNIT)

主要构成: 由十六组拨动开关及显示灯,用来指示逻辑电平。注意:当显示灯亮时表示逻辑低电平,灭时表示逻辑高电平。

17. 单脉冲触发单元(KK UNIT)

主要构成:包括两个单脉冲触发器,由74LS00芯片和微动开关等构成两路

R-S触发器。单脉冲输出分上跳和下跳,分别以“+”和“-“表

示,其输出KKI'和KK2'是未经过消抖电路的输出端。

18. 信号源单元(SIGNAL UNIT)

19. 转接母线

主要构成: 此单元由10组排针引线,圆孔单股导线插座组成,用于将排针形

式的电路引脚和单股导线形式的引脚相互转换。从而为各实验

单元的相互配合使用提供方便。

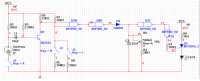

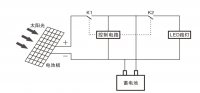

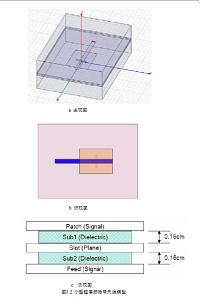

2.2.2 PCI总线扩展卡单元结构及其功能

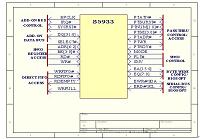

主要芯片及其结构: AMCC S5933芯片,24C16芯片,系统芯片。

主要功能: 实现PCI总线到ADD-ON总线的转换,并进行电

路初始化工作。

2.3 32位微机实验系统的三种总线

2.3.1 PCI总线接口信号概述

1. 地址和数据信号线:

AD[31:0] t/s PCI局部总线的地址/数据线.这些管脚位为地址数据所复用。每一个总线操作都包含了一个地址相位和一个或多个数据相位。当FRAME#有效时,表示地址相位。当IRDy#和JDRY#同时有效时,表示数据相位。

C/BE[3:0]# t/s 总线命令和字节使能。复用信号线。在一个地址相位的总线操作之后,这些管脚产生0总线命令。在一个数据相位之后,管脚被用来充当字节使能,说明数据线上的那些字节有效。

PAR t/s 奇偶校验。是对AD[31:0]和C/BE[0:3]#进行校验的。在

地址相位后的一个周期内由控制者发出稳定的PAR。在一个写

数据操作之后,紧跟着IRDY#激活信号,总线控制发出一个PAR信号。在一个读数据操作之后,紧跟着JDRY#激活信号,从设备发出一个PAR信号。信号延迟一个时钟周期。

2. 接口控制信号线:

FRAME# s/t/s 帧周取信号.该信号由当前总线控制,标识了一个总线

操作的开始和持续。一开始产生的信号表示了一次总线传的

开始,而且有效的地址信号和对应的总线命令产生。在总线操

作的数据传输部分该信号的保持,当信号无效说明进入最后一个数据相位。

IRDY# s/t/s 主设备Ready。该信号由总线控制者发出,表示总线控

制者可以完成当前的数据相位。对写操作,他表示AD[31:0]上的数据有效。当IRDY#和TRDY#同时有效时,数据传输才能进行,否则进入等待状态。

TRDY# s/t/s 从设备Ready。该信号由从设备发出,表示从设备可以

完成当前的数据相位。对读操作,他表示从设备在AD[31:0]上提供了有效的数据。当IRDY#和TRDY#同时有效时,数据传

输才能进行,否则进入等待状态。

STOP# s/t/s 停止。停止信号由从设备发出,用来向主设备发出停上当前传输的信息。

LOCK# in 锁定。该信号表示要独占资源。S5933可能被某一主设备

锁定当作一个从设备。但当S5933是一个主设备时,S5933下

能被锁定。

IDSEL in 初始化设备选择。在配制读写操作时,该信号为片选信号。

DEVSEL# s/t/s 设备选择。该信号由一个激活的从设备发出,译码为地

址和总线指令有效。对于主设备, 它表示是否有设备对当前

时钟周期进行译码。错误反应信号线:

PERR# s/t/s 校验错。这信号报告了除特殊周期外其他任何周期在总线传输的数据相位中出现校验错误。

SERR# o/d 系统错。该信号用来报告地址奇偶错。特殊命令周期中的数据奇偶错以及任何错误可能引起灾难性后果的系统错误。仲裁信号线:

REQ# out 请求信号。该信号由一个想要成为主控的设备发出。他是

一个点对点的信号并且每一个设备都有自己的 REQ

GNT# in 应答信号。是一个点对点的允许信号,表示每一个潜在的设备已经取得了控制总线的权利。

3. 系统信号线:

CLK# in 时钟信号。除了RST#和 IRQA#,CLK对所有信号上升沿有效。其频率最高为 33MHZ,最低为DC(0HZ)。

RST# in 复位。将信号复位到一个已知的状态。所有的PCI总线的

输出接口信号不能被驱动,而把极开路信号象SERR#被置为高

阻状态。

4. 中断信号线:

INTA# o/d 中断A。该信号是一个电平触发,低电平有效的信号。

微信

QQ1:3097331788 QQ2:2601997959 QQ3:2993773635